# ESP32-C61

## 系列芯片勘误表 Version v1.0

# 目录

|                               |   |

|-------------------------------|---|

| 目录                            | i |

| 1 芯片版本标识                      | 1 |

| 1.1 芯片版本编号                    | 1 |

| 1.2 主要标识方式                    | 1 |

| 1.3 其他标识方式                    | 3 |

| 1.4 ESP-IDF 支持版本              | 4 |

| 1.5 相关文档                      | 5 |

| 2 勘误表                         | 5 |

| 3 所有错误描述                      | 5 |

| 3.1 [CPU-718] PSRAM 先写后读一致性问题 | 5 |

| 4 修订历史                        | 6 |

| 5 相关文档和资源                     | 6 |

| 5.1 相关文档                      | 6 |

| 5.2 开发者社区                     | 6 |

| 5.3 产品                        | 7 |

| 5.4 联系我们                      | 7 |

| 6 免责声明和版权公告                   | 7 |

# 1 芯片版本标识

乐鑫引入了新的 **vM.X** 编号方案来表示芯片的修订版本。本指南概述了该编号方案的含义，并介绍了芯片版本的其他各类标识。

## 1.1 芯片版本编号

乐鑫使用 **vM.X** 编码方式表示芯片版本 (Chip Revision)。

**M** – 主版本号，表示芯片修订的主要版本。该号码变更表示在旧版芯片上使用的软件与新版芯片不兼容，需要升级软件方可使用。

**X** – 次版本号，表示芯片修订的次要版本。该号码变更表示在旧版芯片上使用的软件与新版芯片兼容，无需升级软件。

**vM.X** 编码方式将取代旧的编码方式，包括 ECO 编码、Vxxx 编码等。

## 1.2 主要标识方式

### eFuse 位

芯片版本使用两个 eFuse 字段编码：

- EFUSE\_RD\_MAC\_SYS2\_REG[3:0]

- EFUSE\_RD\_MAC\_SYS2\_REG[5:4]

表 1.1: eFuse 版本标示位

|      | 标示位                      | 芯片版本 |      |      |      |

|------|--------------------------|------|------|------|------|

|      |                          | v0.0 | v0.1 | v0.2 | v1.0 |

| 主版本号 | EFUSE_RD_MAC_SYS2_REG[5] | 0    | 0    | 0    | 0    |

|      | EFUSE_RD_MAC_SYS2_REG[4] | 0    | 0    | 0    | 1    |

| 次版本号 | EFUSE_RD_MAC_SYS2_REG[3] | 0    | 0    | 0    | 0    |

|      | EFUSE_RD_MAC_SYS2_REG[2] | 0    | 0    | 0    | 0    |

|      | EFUSE_RD_MAC_SYS2_REG[1] | 0    | 0    | 1    | 0    |

|      | EFUSE_RD_MAC_SYS2_REG[0] | 0    | 1    | 0    | 0    |

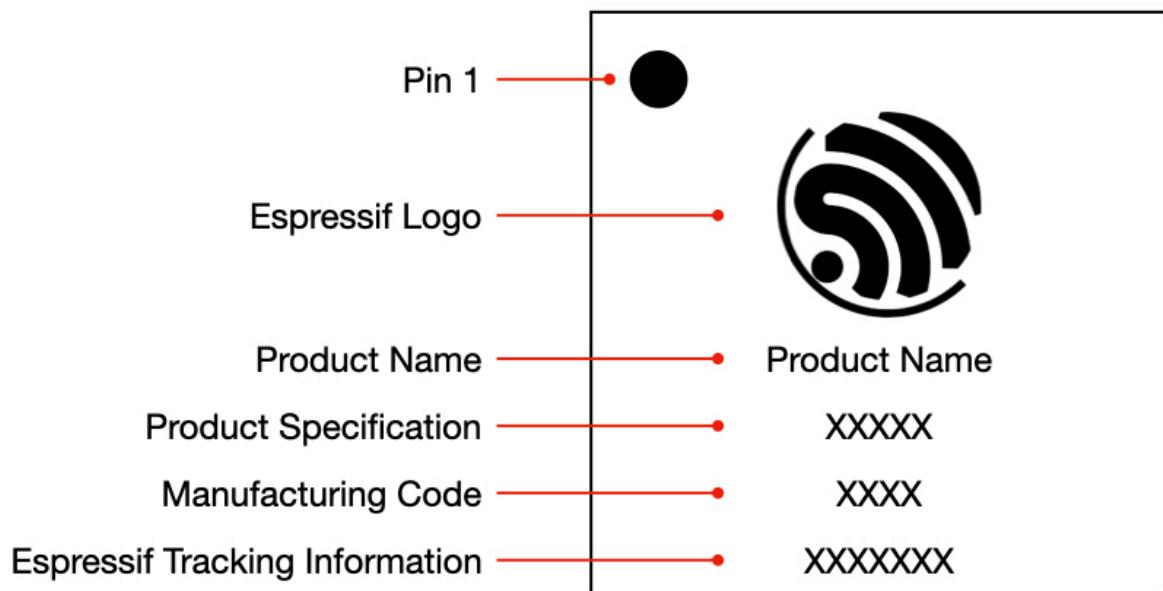

### 芯片标识

- 芯片丝印的 **Manufacturing Code** (生产编码) 行

图 1.1: 芯片丝印示意图

表 1.2: 芯片丝印芯片版本标识

| 芯片版本 | 生产编码   |

|------|--------|

| v0.0 | X A XX |

| v0.1 | X B XX |

| v0.2 | X C XX |

| v1.0 | X D XX |

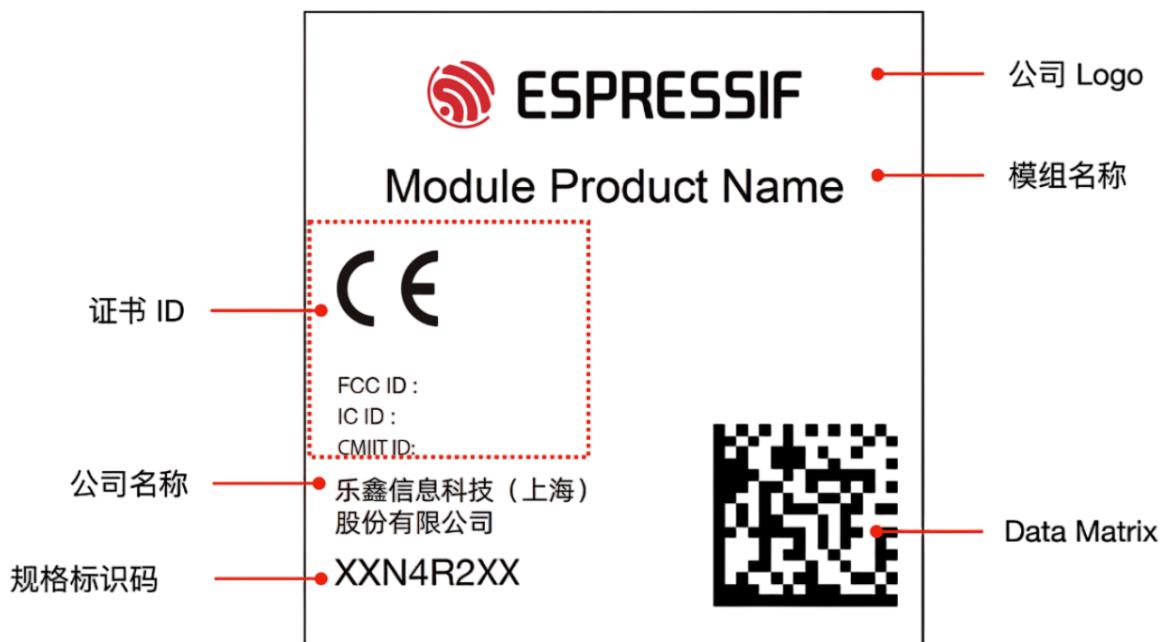

### 模组标识

- 模组丝印的 规格标识码行

图 1.2: 模组丝印示意图

表 1.3: 模组丝印芯片版本标识

| 芯片版本 | 规格标识码   |

|------|---------|

| v0.0 | XA XXXX |

| v0.1 | MB XXXX |

| v0.2 | MC XXXX |

| v1.0 | MD XXXX |

### 1.3 其他标识方式

#### 日期代码

有些芯片错误不需要在晶圆片上修复，即不需要引入新的芯片版本。

此时，芯片可通过丝印中的 **Date Code**（日期代码）来识别，如图[芯片标识](#)。更多信息，请参考[ESP32-C61 芯片包装信息 > 芯片丝印](#)。

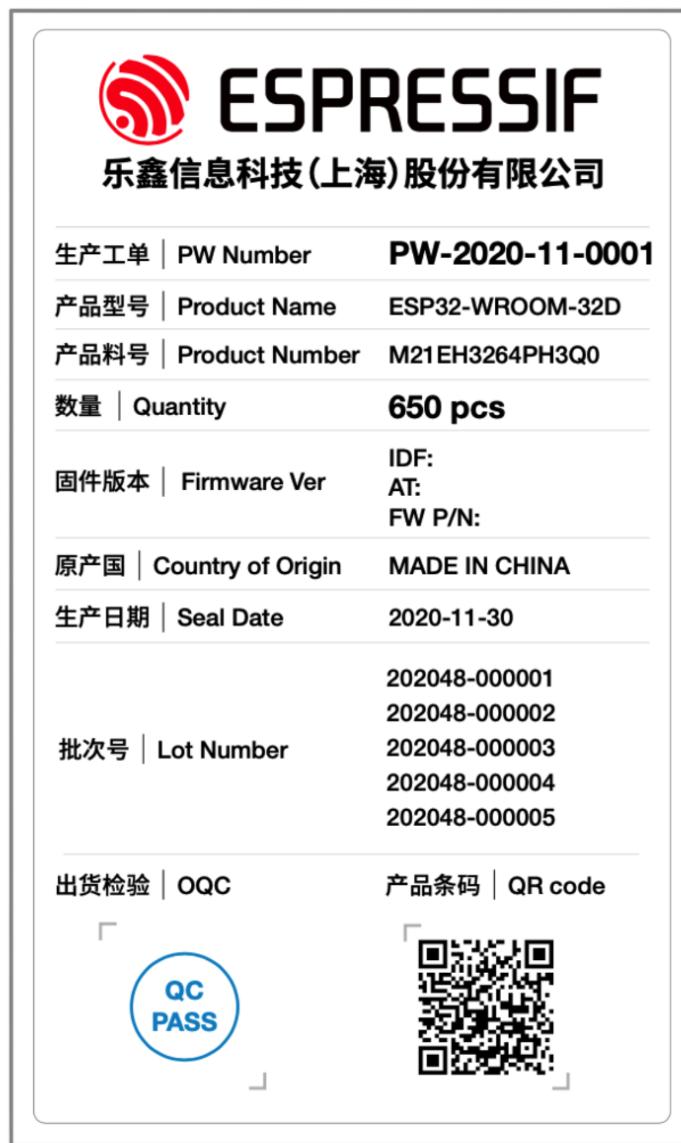

#### 生产工单

内置芯片的模组可通过物料标签中的 **生产工单 (PW Number)** 来识别，如图[模组物料标签](#)。更多信息，请参考[ESP32-C61 模组包装信息 > 披萨盒](#)。

图 1.3: 模组物料标签

备注: 注意, 仅装在铝箔袋中的模组卷盘含有 生产工单 (PW Number) 信息。

## 1.4 ESP-IDF 支持版本

关于特定芯片版本的 ESP-IDF 支持版本, 请参考 [ESP-IDF 版本与乐鑫芯片版本兼容性](#)。

## 1.5 相关文档

- 更多关于芯片版本升级及识别系列产品版本的信息, 请参考 [ESP32-C61 产品/工艺变更通知 \(PCN\)](#)。

- 芯片版本的编码策略, 请参考 [关于芯片版本 \(Chip Revision\) 编码方式的兼容性公告](#)。

## 2 勘误表

表 2.1: 勘误表

| 类别         | 勘误编号    | 描述                                        | 影响版本 |      |      |      |

|------------|---------|-------------------------------------------|------|------|------|------|

|            |         |                                           | v0.0 | v0.1 | v0.2 | v1.0 |

| RISC-V CPU | CPU-718 | <a href="#">[CPU-718] PSRAM 先写后读一致性问题</a> | Y    | Y    | Y    | Y    |

## 3 所有错误描述

### 3.1 [CPU-718] PSRAM 先写后读一致性问题

影响版本: v0.0 v0.1 v0.2 v1.0

#### 描述

当 CPU 通过 CACHE 或 DMA 对 PSRAM 进行随机读写时, 如果满足以下任一条件, 可能会出现 CPU 访问 PSRAM 的数据一致性问题:

- PSRAM 加密或解密已启用, 或

- 通过 DMA 访问 PSRAM 时, AHB\_DMA\_OUT\_DATA\_BURST\_MODE\_SEL\_CHn 配置为 0 或 1

**原因** MSPI 硬件负责管理 CPU 对 PSRAM 的读写请求, 并且内部存在缓存。因此, MSPI 接收到的 CPU 读写请求并不一定会立即作为 SPI 事务提交到 PSRAM。

如果 CPU 在很短时间内先对某一 PSRAM 物理地址执行写操作, 又立即对相同地址执行读操作, 先发出的写操作可能因 MSPI 内部缓存或加解密延迟而尚未完成; 结果 MSPI 可能先执行后发出的读操作, 导致读取到过期或不一致的数据。

#### 示例

- 当 CACHE 从启用加解密的 PSRAM 区间读取且发生 cache miss 时, 回写的数据可能不一致。

- 在 DMA 写入 PSRAM 完成后, 随即进行的 DMA 读或 CACHE 读同一 PSRAM 区域可能返回不一致的数据。

### 变通方法

- 针对因加解密导致的 cache miss 引起的数据一致性问题：在存在随机读写访问的场景下，不建议启用 PSRAM 加密功能。

- 针对 CPU 通过 DMA 访问时出现的数据一致性问题：在 DMA 写入完成后，或在 CPU 读取相同物理地址之前，增加延时，以确保 MSPI 已实际完成对 PSRAM 的写入操作。

### 解决方案

预计将在下个芯片版本中修复。

## 4 修订历史

表 4.1: 修订历史

| 日期         | 版本   | 发布说明 |

|------------|------|------|

| 2025-11-20 | v1.0 | 首次发布 |

## 5 相关文档和资源

### 5.1 相关文档

- 《ESP32-C61 技术规格书》 - 提供 ESP32-C61 芯片的硬件技术规格。

- 《ESP32-C61 技术参考手册》 - 提供 ESP32-C61 芯片的存储器和外设的详细使用说明。

- 《ESP32-C61 硬件设计指南》 - 提供基于 ESP32-C61 芯片的产品设计规范。

- 证书

<https://espressif.com/zh-hans/support/documents/certificates>

- ESP32-C61 产品/工艺变更通知 (PCN)

<https://espressif.com/zh-hans/support/documents/pcns?keys=ESP32-C61>

- ESP32-C61 公告 - 提供有关安全、bug、兼容性、器件可靠性的信息。

<https://espressif.com/zh-hans/support/documents/advisories?keys=ESP32-C61>

- 文档更新和订阅通知

<https://espressif.com/zh-hans/support/download/documents>

### 5.2 开发者社区

- ESP32-C61 ESP-IDF 编程指南 - ESP-IDF 开发框架的文档中心。

- ESP-IDF 及 GitHub 上的其它开发框架

<https://github.com/espressif>

- ESP32 论坛-工程师对工程师 (E2E) 的社区，您可以在这里提出问题、解决问题、分享知识、探索观点。

<https://esp32.com/>

- The ESP Journal -分享乐鑫工程师的最佳实践、技术文章和工作随笔。

<https://blog.espressif.com/>

- SDK 和演示、App、工具、AT 等下载资源

<https://espressif.com/zh-hans/support/download/sdks-demos>

### 5.3 产品

- ESP32-C61 系列芯片-ESP32-C61 全系列芯片。

<https://espressif.com/zh-hans/products/socs?id=ESP32-C61>

- ESP32-C61 系列模组-ESP32-C61 全系列模组。

<https://espressif.com/zh-hans/products/modules?id=ESP32-C61>

- ESP32-C61 系列开发板-ESP32-C61 全系列开发板。

<https://espressif.com/zh-hans/products/devkits?id=ESP32-C61>

- ESP Product Selector (乐鑫产品选型工具)-通过筛选性能参数、进行产品对比快速定位您所需要的产品。

<https://products.espressif.com/#/product-selector>

### 5.4 联系我们

- 商务问题、技术支持、电路原理图 & PCB 设计审阅、购买样品 (线上商店)、成为供应商、意见与建议

<https://espressif.com/zh-hans/contact-us/sales-questions>

## 6 免责声明和版权公告

本文档中的信息，包括供参考的 URL 地址，如有变更，恕不另行通知。

本文档可能引用了第三方的信息，所有引用的信息均为“按现状”提供，乐鑫不对信息的准确性、真实性做任何保证。

乐鑫不对本文档的内容做任何保证，包括内容的适销性、是否适用于特定用途，也不提供任何其他乐鑫提案、规格书或样品在他处提到的任何保证。

乐鑫不对本文档是否侵犯第三方权利做任何保证，也不对使用本文档内信息导致的任何侵犯知识产权的行为负责。本文档在此未以禁止反言或其他方式授予任何知识产权许可，不管是明示许可还是暗示许可。

Wi-Fi 联盟成员标志归 Wi-Fi 联盟所有。蓝牙标志是 Bluetooth SIG 的注册商标。

文档中提到的所有商标名称、商标和注册商标均属其各自所有者的财产，特此声明。