数模转换器 (DAC)

概况

ESP32-S2 有两个 8 位数模转换器 (DAC) 通道,分别连接到 GPIO17(通道 1)和 GPIO18(通道 2)。每个 DAC 通道可以将数字值 0~255 转换成模拟电压 0~Vref(此处的 Vref 为 VDD3P3_RTC_IO 引脚输入的参考电压,一般来说其输入的电压值应等于电源电压 VDD)。输出电压可按以下方式计算:

out_voltage = Vref * digi_val / 255

DAC 外设支持以下列方式输出模拟信号:

直接输出电压。DAC 通道持续输出某一指定电压。

通过 DMA 输出连续模拟信号。DAC 以某一特定频率转换缓冲器中的数据。

通过余弦波发生器输出余弦波。DAC 通道可以输出特定频率和振幅的余弦波。

其他模拟输出选项可参考 Sigma-Delta 调制 和 LED PWM 控制器。这两个模块均输出高频的 PWM/PDM 信号,也可借助硬件低通滤波输出较低频率的模拟信号。

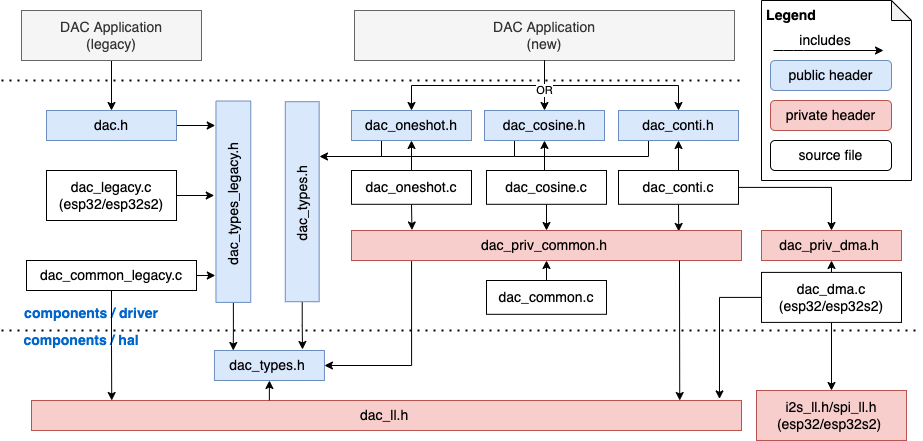

DAC 文件结构

DAC 文件结构

需包含在 DAC 应用程序中的公共头文件包括:

dac.h:原有 DAC 驱动的最上层头文件,只包含在使用原有驱动 API 的应用程序中。dac_oneshot.h:新 DAC 驱动的最上层头文件,应包含在使用新驱动 API(单次模式)的应用程序中。dac_cosine.h:新 DAC 驱动的最上层头文件,应包含在使用新驱动 API(余弦模式)的应用程序中。dac_continuous.h:新 DAC 驱动的最上层头文件,应包含在使用新驱动 API(连续模式)的应用程序中。

备注

原有驱动程序与新驱动程序无法共存。使用原有驱动需包含 dac.h,使用新驱动需包含 dac_oneshot.h、 dac_cosine.h 和 dac_continuous.h。后续更新或将移除原有驱动程序。

功能概览

资源管理

ESP32-S2 有两个 DAC 通道。通道的软件资源互相独立,用户可以根据具体情况调用 dac_oneshot_handle_t、 dac_cosine_handle_t 或 dac_continuous_handle_t 来管理不同通道,但不支持在同一个通道上注册不同模式。

电压直接输出(单次/直接模式)

在这种模式下,DAC 通道每次调用 dac_oneshot_output_voltage() (可在 ISR 中调用)时都可以将一个 8 位数字转换为模拟值。直至下一次转换开始前,DAC 通道上都将维持该模拟电压。开始转换电压前,需要首先调用 dac_oneshot_new_channel() 来启用该 DAC 通道。

连续波输出(连续/DMA 模式)

DAC 通道可以通过 DMA 连续转换数字信号,这种模式下有三种写入 DAC 数据的方法:

常规写入(同步):一次性传输所有数据并在所有数据均已载入 DMA 缓冲区前保持阻塞状态。如果不再继续输入数据,电压将维持在最后的转换值。该模式通常用于传输音频等长信号。要连续转换数据,需要调用

dac_continuous_new_channels()来分配连续通道句柄,调用dac_continuous_enable()来启用 DMA 转换,然后调用dac_continuous_write()来同步写入数据。示例可参考 peripherals/dac/dac_continuous/dac_audio。循环写入:在数据载入 DMA 缓冲区后,缓冲区中的数据将以非阻塞的方式被循环转换。但要注意,输入的缓冲区大小受 DMA 描述符数量和 DMA 缓冲区大小的限制。该模式通常用于传输如正弦波等需要重复的短信号。为了启用循环写入,需要在启用 DAC 连续模式后调用

dac_continuous_write_cyclically()。示例可参考 peripherals/dac/dac_continuous/signal_generator。异步写入。可根据事件回调异步传输数据。需要调用

dac_event_callbacks_t::on_convert_done以启用异步模式。用户在回调中可得到dac_event_data_t,其中包含 DMA 缓冲区的地址和长度,即允许用户直接将数据载入 DMA 缓冲区。启用异步写入前需要调用dac_continuous_register_event_callback()、dac_event_callbacks_t::on_convert_done和dac_continuous_start_async_writing()。注意,异步写入一旦开始,回调函数将被持续触发。调用dac_continuous_write_asynchronously()可以在某个单独任务中或直接在回调函数中载入数据。示例可参考 peripherals/dac/dac_continuous/dac_audio。

在 ESP32-S2 上,DAC 的数字控制器可以在内部连接到 SPI3,并借用其 DMA 进行连续转换。

DAC 的数字控制器的时钟源包括:

dac_continuous_digi_clk_src_t::DAC_DIGI_CLK_SRC_APB支持 77 Hz 到若干 MHz 之间的频率。该时钟源为默认时钟源,也可通过选择dac_continuous_digi_clk_src_t::DAC_DIGI_CLK_SRC_DEFAULT来启用该时钟源。dac_continuous_digi_clk_src_t::DAC_DIGI_CLK_SRC_APLL支持 6 Hz 到若干 MHz 之间的频率。该时钟源可能会被其他外设占用,导致无法提供所需频率。该时钟源可能会被其他外设占用而导致频率无法更改,此时除非 APLL 仍能准确分频得到 DAC DMA 的目标频率,否则将无法使用该时钟源。

余弦波输出(余弦模式)

DAC 外设中包含一个余弦波发生器,可以在通道上产生余弦波。用户可以配置余弦波的频率、振幅和相位。启用该模式需要先调用 dac_cosine_new_channel() 将 DAC 转换成余弦模式,然后调用 dac_cosine_start() 启动余弦波发生器。

目前,余弦波发生器仅有 RTC_FAST 一个时钟源,可通过选择 dac_cosine_clk_src_t::DAC_COSINE_CLK_SRC_RTC_FAST 来启用该时钟源。该时钟源为默认时钟源,与 dac_cosine_clk_src_t::DAC_COSINE_CLK_SRC_RTC_DEFAULT 相同。

电源管理

启用电源管理时(即开启 CONFIG_PM_ENABLE),系统会在进入 Light-sleep 模式前调整或停止 DAC 时钟源,这可能会影响 DAC 信号,从而导致数据无法正确转换。

在连续模式下使用 DAC 驱动时,可以通过获取电源管理锁来防止系统在 DMA 或余弦波模式下改变或停止时钟源。时钟源为 APB 时,锁的类型将被设置为 esp_pm_lock_type_t::ESP_PM_APB_FREQ_MAX。时钟源为 APLL 时(仅在 DMA 模式下),锁的类型将被设置为 esp_pm_lock_type_t::ESP_PM_NO_LIGHT_SLEEP。在进行 DAC 转换时(即 DMA 或余弦波发生器运行时),驱动程序会保证在调用 dac_continuous_enable() 后获取电源管理锁。同样地,在调用 dac_continuous_disable() 时,驱动程序会释放锁。

IRAM 安全

默认情况下,由于写入或擦除 flash 等原因导致 cache 被禁用时,DAC 的 DMA 中断将产生延迟,无法及时执行 DMA EOF 中断。

在实时应用中,可通过启用 Kconfig 选项 CONFIG_DAC_ISR_IRAM_SAFE 来避免此种情况发生,启用后:

即使在 cache 被禁用的情况下,也可以启用中断服务。

驱动对象会被放入 DRAM(以防其被意外链接到 PSRAM)。

此时在 cache 被禁用时仍可以运行中断,但会增加 IRAM 内存消耗。

线程安全

驱动程序可保证所有公共 DAC API 的线程安全,用户可以从不同的 RTOS 任务中调用这些 API,而不需要额外的锁来保护。注意,DAC 驱动使用 mutex 锁来保证线程安全,因此不允许在 ISR 中使用除了 dac_oneshot_output_voltage() 之外的 API。

Kconfig 选项

CONFIG_DAC_ISR_IRAM_SAFE 控制默认 ISR 处理程序在 cache 被禁用时能否继续运行。更多信息可参考 IRAM 安全。

CONFIG_DAC_SUPPRESS_DEPRECATE_WARN 控制是否在使用原有 DAC 驱动时关闭警告信息。

CONFIG_DAC_ENABLE_DEBUG_LOG 用于启用调试日志输出。启用该选项将增加固件的二进制文件大小。

应用示例

单次模式、 连续模式 和 余弦模式 的基本示例如下所示:

API 参考

Header File

Functions

-

esp_err_t dac_oneshot_new_channel(const dac_oneshot_config_t *oneshot_cfg, dac_oneshot_handle_t *ret_handle)

Allocate a new DAC oneshot channel.

备注

The channel will be enabled as well when the channel allocated

- 参数

oneshot_cfg – [in] The configuration for the oneshot channel

ret_handle – [out] The returned oneshot channel handle

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The DAC channel has been registered already

ESP_ERR_NO_MEM No memory for the DAC oneshot channel resources

ESP_OK Allocate the new DAC oneshot channel success

-

esp_err_t dac_oneshot_del_channel(dac_oneshot_handle_t handle)

Delete the DAC oneshot channel.

备注

The channel will be disabled as well when the channel deleted

- 参数

handle – [in] The DAC oneshot channel handle

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The channel has already been de-registered

ESP_OK Delete the oneshot channel success

-

esp_err_t dac_oneshot_output_voltage(dac_oneshot_handle_t handle, uint8_t digi_value)

Output the voltage.

备注

Generally it’ll take 7~11 us on ESP32 and 10~21 us on ESP32-S2

- 参数

handle – [in] The DAC oneshot channel handle

digi_value – [in] The digital value that need to be converted

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_OK Convert the digital value success

Structures

-

struct dac_oneshot_config_t

DAC oneshot channel configuration.

Public Members

-

dac_channel_t chan_id

DAC channel id

-

dac_channel_t chan_id

Type Definitions

-

typedef struct dac_oneshot_s *dac_oneshot_handle_t

DAC oneshot channel handle

Header File

Functions

-

esp_err_t dac_cosine_new_channel(const dac_cosine_config_t *cos_cfg, dac_cosine_handle_t *ret_handle)

Allocate a new DAC cosine wave channel.

备注

Since there is only one cosine wave generator, only the first channel can set the frequency of the cosine wave. Normally, the latter one is not allowed to set a different frequency, but the it can be forced to set by setting the bit

force_set_freqin the configuration, notice that another channel will be affected as well when the frequency is updated.- 参数

cos_cfg – [in] The configuration of cosine wave channel

ret_handle – [out] The returned cosine wave channel handle

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The DAC channel has been registered already

ESP_ERR_NO_MEM No memory for the DAC cosine wave channel resources

ESP_OK Allocate the new DAC cosine wave channel success

-

esp_err_t dac_cosine_del_channel(dac_cosine_handle_t handle)

Delete the DAC cosine wave channel.

- 参数

handle – [in] The DAC cosine wave channel handle

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The channel has already been deregistered

ESP_OK Delete the cosine wave channel success

-

esp_err_t dac_cosine_start(dac_cosine_handle_t handle)

Start outputting the cosine wave on the channel.

- 参数

handle – [in] The DAC cosine wave channel handle

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The channel has been started already

ESP_OK Start the cosine wave success

-

esp_err_t dac_cosine_stop(dac_cosine_handle_t handle)

Stop outputting the cosine wave on the channel.

- 参数

handle – [in] The DAC cosine wave channel handle

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The channel has been stopped already

ESP_OK Stop the cosine wave success

Structures

-

struct dac_cosine_config_t

DAC cosine channel configurations.

Public Members

-

dac_channel_t chan_id

The cosine wave channel id

-

uint32_t freq_hz

The frequency of cosine wave, unit: Hz. The cosine wave generator is driven by RTC_FAST clock which is divide from RC_FAST, With the default RTC clock, the minimum frequency of cosine wave is about 130 Hz, Although it can support up to several MHz frequency theoretically, the waveform will distort at high frequency due to the hardware limitation. Typically not suggest to set the frequency higher than 200 KHz

-

dac_cosine_clk_src_t clk_src

The clock source of the cosine wave generator, currently only support

DAC_COSINE_CLK_SRC_DEFAULT

-

dac_cosine_atten_t atten

The attenuation of cosine wave amplitude

-

dac_cosine_phase_t phase

The phase of cosine wave, can only support DAC_COSINE_PHASE_0 or DAC_COSINE_PHASE_180, default as 0 while setting an unsupported phase

-

int8_t offset

The DC offset of cosine wave

-

bool force_set_freq

Force to set the cosine wave frequency

-

struct dac_cosine_config_t::[anonymous] flags

Flags of cosine mode

-

dac_channel_t chan_id

Type Definitions

-

typedef struct dac_cosine_s *dac_cosine_handle_t

DAC cosine wave channel handle

Header File

Functions

-

esp_err_t dac_continuous_new_channels(const dac_continuous_config_t *cont_cfg, dac_continuous_handle_t *ret_handle)

Allocate new DAC channels in continuous mode.

备注

The DAC channels can’t be registered to continuous mode separately

- 参数

cont_cfg – [in] Continuous mode configuration

ret_handle – [out] The returned continuous mode handle

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The DAC channel has been registered already

ESP_ERR_NOT_FOUND Not found the available dma peripheral, might be occupied

ESP_ERR_NO_MEM No memory for the DAC continuous mode resources

ESP_OK Allocate the new DAC continuous mode success

-

esp_err_t dac_continuous_del_channels(dac_continuous_handle_t handle)

Delete the DAC continuous handle.

- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The channels have already been deregistered or not disabled

ESP_OK Delete the continuous channels success

-

esp_err_t dac_continuous_enable(dac_continuous_handle_t handle)

Enabled the DAC continuous mode.

备注

Must enable the channels before

- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The channels have been enabled already

ESP_OK Enable the continuous output success

-

esp_err_t dac_continuous_disable(dac_continuous_handle_t handle)

Disable the DAC continuous mode.

- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The channels have been enabled already

ESP_OK Disable the continuous output success

-

esp_err_t dac_continuous_write(dac_continuous_handle_t handle, uint8_t *buf, size_t buf_size, size_t *bytes_loaded, int timeout_ms)

Write DAC data continuously.

备注

The data in buffer will only be converted one time, This function will be blocked until all data loaded or timeout then the DAC output will keep outputting the voltage of the last data in the buffer

备注

Specially, on ESP32, the data bit width of DAC continuous data is fixed to 16 bits while only the high 8 bits are available, The driver will help to expand the inputted buffer automatically by default, you can also align the data to 16 bits manually by clearing

CONFIG_DAC_DMA_AUTO_16BIT_ALIGNin menuconfig.- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

buf – [in] The digital data buffer to convert

buf_size – [in] The buffer size of digital data buffer

bytes_loaded – [out] The bytes that has been loaded into DMA buffer, can be NULL if don’t need it

timeout_ms – [in] The timeout time in millisecond, set a minus value means will block forever

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The DAC continuous mode has not been enabled yet

ESP_ERR_TIMEOUT Waiting for semaphore or message queue timeout

ESP_OK Success to output the acyclic DAC data

-

esp_err_t dac_continuous_write_cyclically(dac_continuous_handle_t handle, uint8_t *buf, size_t buf_size, size_t *bytes_loaded)

Write DAC continuous data cyclically.

备注

The data in buffer will be converted cyclically using DMA once this function is called, This function will return once the data loaded into DMA buffers.

备注

The buffer size of cyclically output is limited by the descriptor number and dma buffer size while initializing the continuous mode. Concretely, in order to load all the data into descriptors, the cyclic buffer size is not supposed to be greater than

desc_num * buf_size备注

Specially, on ESP32, the data bit width of DAC continuous data is fixed to 16 bits while only the high 8 bits are available, The driver will help to expand the inputted buffer automatically by default, you can also align the data to 16 bits manually by clearing

CONFIG_DAC_DMA_AUTO_16BIT_ALIGNin menuconfig.- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

buf – [in] The digital data buffer to convert

buf_size – [in] The buffer size of digital data buffer

bytes_loaded – [out] The bytes that has been loaded into DMA buffer, can be NULL if don’t need it

- 返回

ESP_ERR_INVALID_ARG The input parameter is invalid

ESP_ERR_INVALID_STATE The DAC continuous mode has not been enabled yet

ESP_OK Success to output the acyclic DAC data

-

esp_err_t dac_continuous_register_event_callback(dac_continuous_handle_t handle, const dac_event_callbacks_t *callbacks, void *user_data)

Set event callbacks for DAC continuous mode.

备注

User can deregister a previously registered callback by calling this function and setting the callback member in the

callbacksstructure to NULL.备注

When CONFIG_DAC_ISR_IRAM_SAFE is enabled, the callback itself and functions called by it should be placed in IRAM. The variables used in this function, including the

user_data, should be in the internal RAM as well.- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

callbacks – [in] Group of callback functions, input NULL to clear the former callbacks

user_data – [in] User data, which will be passed to callback functions directly

- 返回

ESP_OK Set event callbacks successfully

ESP_ERR_INVALID_ARG Set event callbacks failed because of invalid argument

-

esp_err_t dac_continuous_start_async_writing(dac_continuous_handle_t handle)

Start the async writing.

备注

When the asynchronous writing start, the DAC will keep outputting ‘0’ until the data are loaded into the DMA buffer. To loaded the data into DMA buffer, ‘on_convert_done’ callback is required, which can be registered by ‘dac_continuous_register_event_callback’ before enabling

- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

- 返回

ESP_OK Start asynchronous writing successfully

ESP_ERR_INVALID_ARG The handle is NULL

ESP_ERR_INVALID_STATE The channel is not enabled or the ‘on_convert_done’ callback is not registered

-

esp_err_t dac_continuous_stop_async_writing(dac_continuous_handle_t handle)

Stop the sync writing.

- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

- 返回

ESP_OK Stop asynchronous writing successfully

ESP_ERR_INVALID_ARG The handle is NULL

ESP_ERR_INVALID_STATE Asynchronous writing has not started

-

esp_err_t dac_continuous_write_asynchronously(dac_continuous_handle_t handle, uint8_t *dma_buf, size_t dma_buf_len, const uint8_t *data, size_t data_len, size_t *bytes_loaded)

Write DAC data asynchronously.

备注

This function can be called when the asynchronous writing started, and it can be called in the callback directly but recommend to writing data in a task, referring to :example:

peripherals/dac/dac_continuous/dac_audio- 参数

handle – [in] The DAC continuous channel handle that obtained from ‘dac_continuous_new_channels’

dma_buf – [in] The DMA buffer address, it can be acquired from ‘dac_event_data_t’ in the ‘on_convert_done’ callback

dma_buf_len – [in] The DMA buffer length, it can be acquired from ‘dac_event_data_t’ in the ‘on_convert_done’ callback

data – [in] The data that need to be written

data_len – [in] The data length the need to be written

bytes_loaded – [out] The bytes number that has been loaded/written into the DMA buffer

- 返回

ESP_OK Write the data into DMA buffer successfully

ESP_ERR_INVALID_ARG NULL pointer

ESP_ERR_INVALID_STATE The channels haven’t start the asynchronous writing

ESP_ERR_NOT_FOUND The param ‘dam_buf’ not match any existed DMA buffer

Structures

-

struct dac_continuous_config_t

DAC continuous channels’ configurations.

Public Members

-

dac_channel_mask_t chan_mask

DAC channels’ mask for selecting which channels are used

-

uint32_t desc_num

The number of DMA descriptor, at least 2 descriptors are required The number of descriptors is directly proportional to the max data buffer size while converting in cyclic output but only need to ensure it is greater than ‘1’ in acyclic output Typically, suggest to set the number bigger than 5, in case the DMA stopped while sending a short buffer

-

size_t buf_size

The DMA buffer size, should be within 32~4092 bytes. Each DMA buffer will be attached to a DMA descriptor, i.e. the number of DMA buffer will be equal to the DMA descriptor number The DMA buffer size is not allowed to be greater than 4092 bytes The total DMA buffer size equal to

desc_num * buf_sizeTypically, suggest to set the size to the multiple of 4

-

uint32_t freq_hz

The frequency of DAC conversion in continuous mode, unit: Hz The supported range is related to the target and the clock source. For the clock

DAC_DIGI_CLK_SRC_DEFAULT: the range is 19.6 KHz to several MHz on ESP32 and 77 Hz to several MHz on ESP32-S2. For the clockDAC_DIGI_CLK_SRC_APLL: the range is 648 Hz to several MHz on ESP32 and 6 Hz to several MHz on ESP32-S2. Typically not suggest to set the frequency higher than 2 MHz, otherwise the severe distortion will appear

-

int8_t offset

The offset of the DAC digital data. Range -128~127

-

dac_continuous_digi_clk_src_t clk_src

The clock source of digital controller, which can affect the range of supported frequency Currently

DAC_DIGI_CLK_SRC_DEFAULTandDAC_DIGI_CLK_SRC_APLLare available

-

dac_continuous_channel_mode_t chan_mode

The channel mode of continuous mode, only take effect when multiple channels enabled, depends converting the buffer alternately or simultaneously

-

dac_channel_mask_t chan_mask

-

struct dac_event_data_t

Event structure used in DAC event queue.

Public Members

-

void *buf

The pointer of DMA buffer that just finished sending

-

size_t buf_size

The writable buffer size of the DMA buffer, equal to ‘dac_continuous_config_t::buf_size’

-

size_t write_bytes

The number of bytes that be written successfully

-

void *buf

-

struct dac_event_callbacks_t

Group of DAC callbacks.

备注

The callbacks are all running under ISR environment

备注

When CONFIG_DAC_ISR_IRAM_SAFE is enabled, the callback itself and functions called by it should be placed in IRAM. The variables used in the function should be in the SRAM as well.

Public Members

-

dac_isr_callback_t on_convert_done

Callback of data conversion done event An event data buffer previously loaded to the driver has been output and converted. The event data includes DMA buffer address and size that just finished converting.

-

dac_isr_callback_t on_stop

Callback of finished sending all the data. All loaded event data buffers are converted. Driver is pending for new data buffers to be loaded. The event data will be NULL in this callback.

-

dac_isr_callback_t on_convert_done

Type Definitions

-

typedef struct dac_continuous_s *dac_continuous_handle_t

DAC continuous channel handle

-

typedef bool (*dac_isr_callback_t)(dac_continuous_handle_t handle, const dac_event_data_t *event, void *user_data)

DAC event callback.

- Param handle

[in] DAC channel handle, created from

dac_continuous_new_channels()- Param event

[in] DAC event data

- Param user_data

[in] User registered context, passed from

dac_continuous_register_event_callback()- Return

Whether a high priority task has been waken up by this callback function

Enumerations

Header File

Type Definitions

-

typedef soc_periph_dac_digi_clk_src_t dac_continuous_digi_clk_src_t

DAC DMA (digitial controller) clock source.

-

typedef soc_periph_dac_cosine_clk_src_t dac_cosine_clk_src_t

DAC cosine wave generator clock source.

Enumerations

-

enum dac_continuous_channel_mode_t

DAC channel work mode in dma mode.

备注

Only take effect when multiple channels enabled.

备注

Assume the data in buffer is ‘A B C D E F’ DAC_CHANNEL_MODE_SIMUL:

channel 0: A B C D E F

channel 1: A B C D E F DAC_CHANNEL_MODE_ALTER:

channel 0: A C E

channel 1: B D F

Values:

-

enumerator DAC_CHANNEL_MODE_SIMUL

The data in the DMA buffer is simultaneously output to the enable channel of the DAC.

-

enumerator DAC_CHANNEL_MODE_ALTER

The data in the DMA buffer is alternately output to the enable channel of the DAC.

Header File

Enumerations

-

enum dac_channel_t

Values:

-

enumerator DAC_CHAN_0

DAC channel 0 is GPIO25(ESP32) / GPIO17(ESP32S2)

-

enumerator DAC_CHAN_1

DAC channel 1 is GPIO26(ESP32) / GPIO18(ESP32S2)

-

enumerator DAC_CHANNEL_1

Alias of ‘DAC_CHAN_0’, now the channel index start from ‘0’

-

enumerator DAC_CHANNEL_2

Alias of ‘DAC_CHAN_1’, now the channel index start from ‘0’

-

enumerator DAC_CHAN_0

-

enum dac_cosine_atten_t

The attenuation of the amplitude of the cosine wave generator. The max amplitude is VDD3P3_RTC.

Values:

-

enumerator DAC_COSINE_ATTEN_DEFAULT

No attenuation to the DAC cosine wave amplitude. Default.

-

enumerator DAC_COSINE_ATTEN_DB_0

Original amplitude of the DAC cosine wave, equals to DAC_COSINE_ATTEN_DEFAULT

-

enumerator DAC_COSINE_ATTEN_DB_6

1/2 amplitude of the DAC cosine wave

-

enumerator DAC_COSINE_ATTEN_DB_12

1/4 amplitude of the DAC cosine wave

-

enumerator DAC_COSINE_ATTEN_DB_18

1/8 amplitude of the DAC cosine wave

-

enumerator DAC_COSINE_ATTEN_DEFAULT