Schematic Checklist

Overview

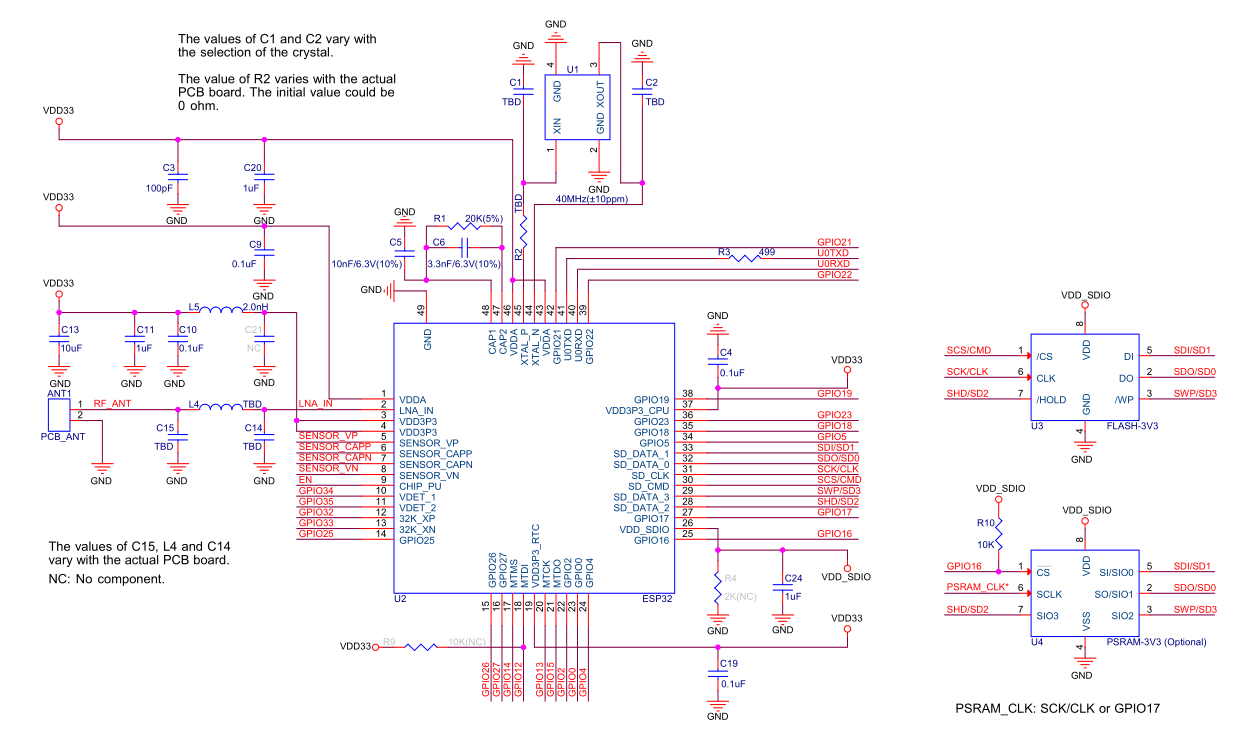

The integrated circuitry of ESP32 requires only 20 electrical components (resistors, capacitors, and inductors) and a crystal, as well as an SPI flash. The high integration of ESP32 allows for simple peripheral circuit design. This chapter details the schematic design of ESP32.

The following figure shows a reference schematic design of ESP32. It can be used as the basis of your schematic design.

ESP32 Reference Schematic

Note that Figure ESP32 Reference Schematic shows the connection method for quad 3.3 V external flash/PSRAM.

The SCLK for PSRAM can be assigned to any available GPIO (configured by software). It is recommended to use GPIO17, or share the clock line with flash, i.e., SD_CLK.

When using ESP32-D0WDR2-V3 (with in-package quad 3.3 V PSRAM), the connection method for external flash is as shown in ESP32 Reference Schematic. GPIO16 needs a pull-up resistor, with a typical value of 10 kΩ.

When using a module with built-in ESP32-D0WDR2-V3, since VDD_SDIO is not led out, the pull-up on GPIO16 needs to be connected to an external 3.3 V power supply. This will result in additional power consumption. If low power consumption is required, use a pull-up resistor of 1 MΩ at the maximum.

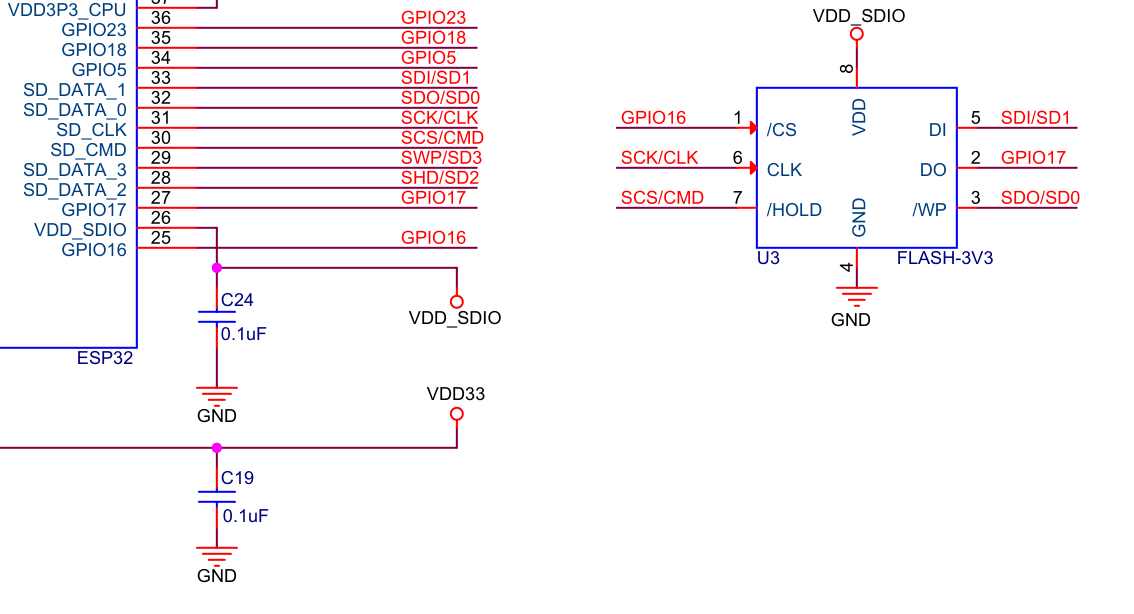

When using ESP32-U4WDH (with built-in quad 3.3 V flash), the internal flash connection is as shown in ESP32 Schematic for Quad 3.3 V In-Package Flash.

When using in-package flash/PSRAM, there is no need to install resistors on the SPI traces, nor to pay special attention to the SPI traces.

Whether R9 needs to be installed should be determined according to the ESP32 Chip Series Datasheet > Section Internal LDO (VDD_SDIO) Voltage Control.

ESP32 Schematic for Quad 3.3 V In-Package Flash

Any basic ESP32 circuit design may be broken down into the following major building blocks:

The rest of this chapter details the specifics of circuit design for each of these sections.

Power Supply

The general recommendations for power supply design are:

When using a single power supply, the recommended power supply voltage is 3.3 V and the output current is no less than 500 mA.

It is suggested to add an ESD protection diode and at least 10 μF capacitor at the power entrance.

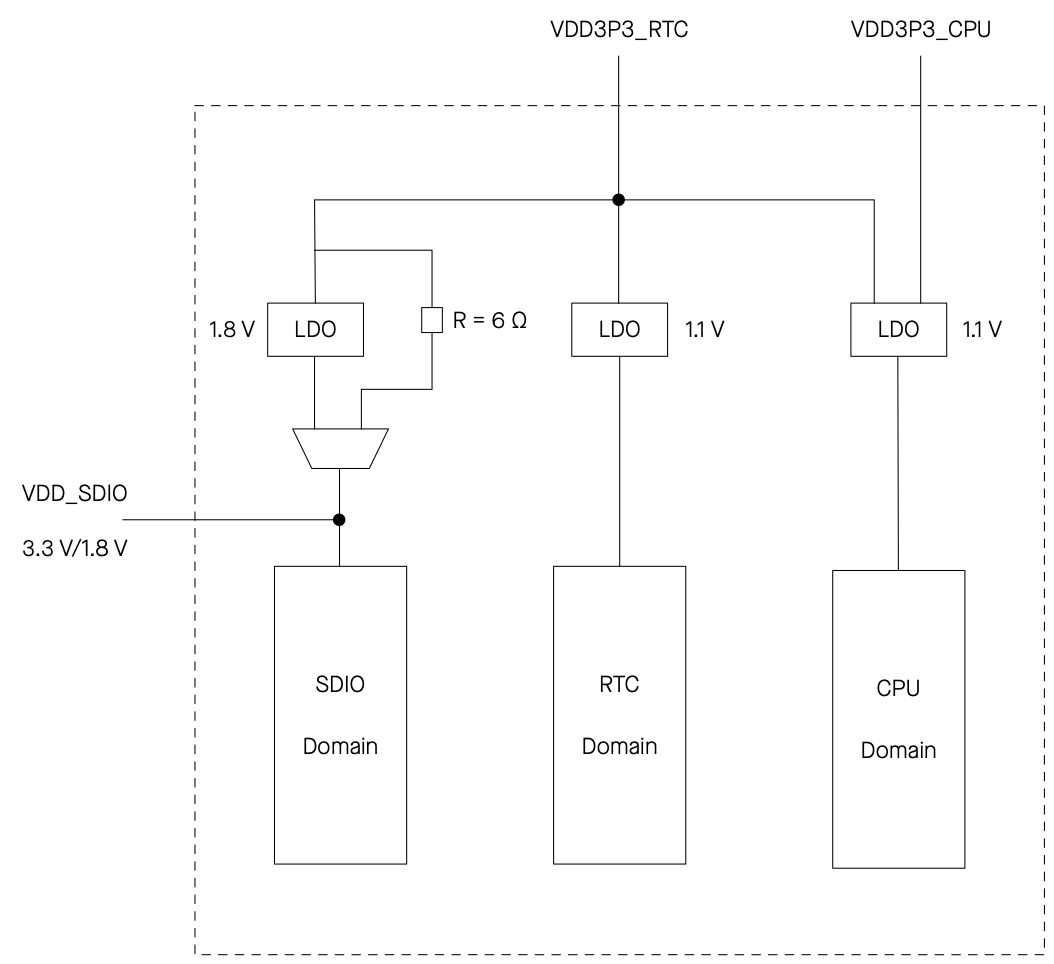

The power scheme is shown in Figure ESP32 Power Scheme.

ESP32 Power Scheme

More information about power supply pins can be found in ESP32 Series Datasheet > Section Power Supply.

Digital Power Supply

ESP32 has pin37 VDD3P3_CPU as the digital power supply pin, with an operating voltage range of 1.8 V ~ 3.6 V. ESP32 also has pin 20 VDD3P3_RTC as the RTC and partial digital power supply pin, with an operating voltage range of 2.3 V ~ 3.6 V. It is recommended to add a 0.1 μF capacitor close to the digital power supply pins in the circuit.

Pin VDD_SDIO serves as the power supply for the external device at either 1.8 V or 3.3 V (default).

When VDD_SDIO is in 1.8 V mode, it is powered by ESP32’s internal LDO, which can provide a maximum current of 40 mA and an output voltage range of 1.65 V ~ 2.0 V. It is recommended to add a 2 kΩ pull-down resistor and a 4.7 μF capacitor to ground at the VDD_SDIO pin.

When VDD_SDIO is in 3.3 V mode, it is powered by VDD3P3_RTC through an internal resistor of about 6 Ω. Therefore, there will be some voltage drop between VDD_SDIO and VDD3P3_RTC. It is recommended to add a 1 μF filter capacitor close to the VDD_SDIO pin.

Attention

When using VDDVDD_SDIO_SPI as the power supply pin for in-package or off-package 3.3 V flash/PSRAM, please ensure that VDD3P3_RTC remains above 3.0 V to meet the operating voltage requirements of the flash/PSRAM, considering the voltage drop mentioned earlier.

Note that VDD3P3_RTC cannot supply power alone; all power supplies must be powered on at the same time.

Depending on the value of EFUSE_SDIO_FORCE, the VDD_SDIO voltage can be controlled in two ways, as Table VDD_SDIO Voltage Control shows.

EFUSE_SDIO_FORCE |

MTDI |

EFUSE_SDIO_TIEH |

Voltage |

VDD_SDIO Power Source |

|---|---|---|---|---|

0 |

0 |

Ignored |

3.3 V |

VDD3P3_RTC via RSPI (default) |

0 |

1 |

Ignored |

1.8 V |

Flash Voltage Regulator |

1 |

Ignored |

0 |

1.8 V |

Flash Voltage Regulator |

1 |

Ignored |

1 |

3.3 V |

VDD3P3_RTC via RSPI |

VDD_SDIO can also be driven by an external power supply.

It is recommended to use the VDD_SDIO output to supply power to external or internal flash/PSRAM.

Analog Power Supply

ESP32’s VDDA (pin 1/43/46) and VDD3P3 (pin 3/4) are the analog power supply pins, working at 2.3 V ~ 3.6 V.

For VDD3P3, when ESP32 is transmitting signals, there may be a sudden increase in the current draw, causing power rail collapse. Therefore, it is highly recommended to add a 10 μF capacitor to the power rail, which can work in conjunction with the 1 μF capacitor(s) or other capacitors.

It is suggested to add an extra 10 μF capacitor at the power entrance. If the power entrance is close to VDD3P3, then two 10 μF capacitors can be merged into one.

Add an LC circuit to the VDD3P3 power rail to suppress high-frequency harmonics. The inductor’s rated current is preferably 500 mA and above.

For the remaining capacitor circuits, please refer to ESP32 Reference Schematic.

Chip Power-up and Reset Timing

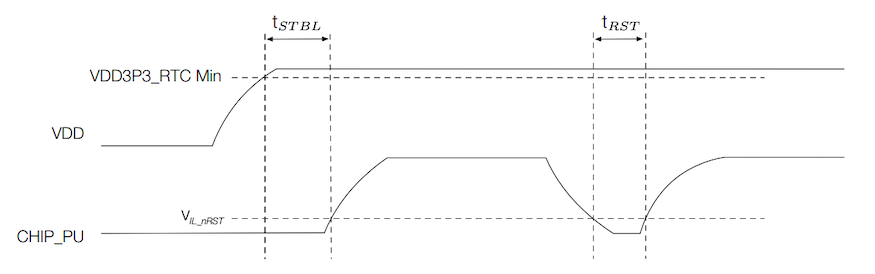

ESP32’s CHIP_PU pin can enable the chip when it is high and reset the chip when it is low.

When ESP32 uses a 3.3 V system power supply, the power rails need some time to stabilize before CHIP_PU is pulled up and the chip is enabled. Therefore, CHIP_PU needs to be asserted high after the 3.3 V rails have been brought up.

To reset the chip, keep the reset voltage VIL_nRST in the range of (NA ~ 0.6) V. To avoid reboots caused by external interferences, make the CHIP_PU trace as short as possible.

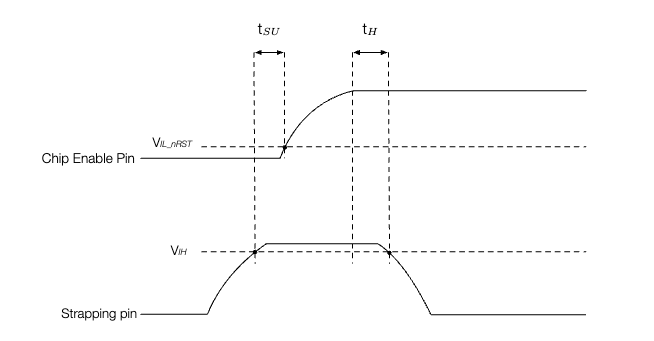

Figure ESP32 Power-up and Reset Timing shows the power-up and reset timing of ESP32.

ESP32 Power-up and Reset Timing

Table Description of Timing Parameters for Power-up and Reset provides the specific timing requirements.

Parameter |

Description |

Minimum (µs) |

|---|---|---|

tSTBL |

Time reserved for the power rails to stabilize before the CHIP_PU pin is pulled high to activate the chip |

50 |

tRST |

Time reserved for CHIP_PU to stay below VIL_nRST to reset the chip |

50 |

Attention

CHIP_PU must not be left floating.

To ensure the correct power-up and reset timing, it is advised to add an RC delay circuit at the CHIP_PU pin. The recommended setting for the RC delay circuit is usually R = 10 kΩ and C = 1 μF. However, specific parameters should be adjusted based on the characteristics of the actual power supply and the power-up and reset timing of the chip.

If the user application has one of the following scenarios:

Slow power rise or fall, such as during battery charging.

Frequent power on/off operations.

Unstable power supply, such as in photovoltaic power generation.

Then, the RC circuit itself may not meet the timing requirements, resulting in the chip being unable to boot correctly. In this case, additional designs need to be added, such as:

Adding an external reset chip or a watchdog chip, typically with a threshold of around 3.0 V.

Implementing reset functionality through a button or the main controller.

Flash and PSRAM

ESP32 requires in-package or off-package flash to store application firmware and data. In-package PSRAM or off-package PSRAM is optional.

In-Package Flash and PSRAM

The tables list the pin-to-pin mapping between the chip and in-package flash/PSRAM. Please note that the following chip pins can connect at most one flash and one PSRAM. That is to say, when there is only flash in the package, the pin occupied by flash can only connect PSRAM and cannot be used for other functions; when there is only PSRAM, the pin occupied by PSRAM can only connect flash; when there are both flash and PSRAM, the pin occupied cannot connect any more flash or PSRAM.

ESP32-U4WDH |

In-Package Flash (4 MB) |

|---|---|

SD_DATA_1 |

IO0/DI |

GPIO17 |

IO1/DO |

SD_DATA_0 |

IO2/WP# |

SD_CMD |

IO3/HOLD# |

SD_CLK |

CLK |

GPIO16 |

CS# |

GND |

VSS |

VDD_SDIO |

VDD |

ESP32-D0WDR2-V3 |

In-Package PSRAM (2 MB) |

|---|---|

SD_DATA_1 |

SIO0/SI |

SD_DATA_0 |

SIO1/SO |

SD_DATA_3 |

SIO2 |

SD_DATA_2 |

SIO3 |

SD_CLK |

SCLK |

GPIO16 |

CE# |

GND |

VSS |

VDD_SDIO |

VDD |

Off-Package Flash and PSRAM

To reduce the risk of software compatibility issues, it is recommended to use flash and PSRAM models officially validated by Espressif. For detailed model selection, consult the sales or technical support team. If VDD_SDIO is used to supply power, make sure to select the appropriate off-package flash and RAM according to the power voltage on VDD_SDIO (1.8 V/3.3 V). It is recommended to add zero-ohm resistor footprints in series on the SPI communication lines. These footprints provide flexibility for future adjustments, such as tuning drive strength, mitigating RF interference, correcting signal timing, and reducing noise, if needed.

Clock Source

ESP32 supports two external clock sources:

External Crystal Clock Source (Compulsory)

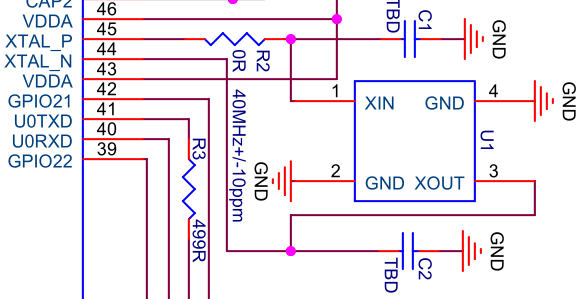

The ESP32 firmware only supports 40 MHz crystal.

The circuit for the crystal is shown in Figure ESP32 Schematic for External Crystal. Note that the accuracy of the selected crystal should be within ±10 ppm.

ESP32 Schematic for External Crystal

Please add a series inductor on the XTAL_P clock trace. Initially, it is suggested to use an inductor of 0 Ω to reduce the impact of high-frequency crystal harmonics on RF performance, and the value should be adjusted after an overall test.

The initial values of external capacitors C1 and C2 can be determined according to the formula:

where the value of CL (load capacitance) can be found in the crystal’s datasheet, and the value of Cstray refers to the PCB’s stray capacitance. The values of C1 and C2 need to be further adjusted after an overall test as below:

Select TX tone mode using the Certification and Test Tool.

Observe the 2.4 GHz signal with a radio communication analyzer or a spectrum analyzer and demodulate it to obtain the actual frequency offset.

Adjust the frequency offset to be within ±10 ppm (recommended) by adjusting the external load capacitance.

When the center frequency offset is positive, it means that the equivalent load capacitance is small, and the external load capacitance needs to be increased.

When the center frequency offset is negative, it means the equivalent load capacitance is large, and the external load capacitance needs to be reduced.

External load capacitance at the two sides are usually equal, but in special cases, they may have slightly different values.

Note

Defects in the manufacturing of crystal (for example, large frequency deviation of more than ±10 ppm, unstable performance within the operating temperature range, etc) may lead to the malfunction of ESP32, resulting in a decrease of the RF performance.

It is recommended that the amplitude of the crystal is greater than 500 mV.

When Wi-Fi or Bluetooth connection fails, after ruling out software problems, you may follow the steps mentioned above to ensure that the frequency offset meets the requirements by adjusting capacitors at the two sides of the crystal.

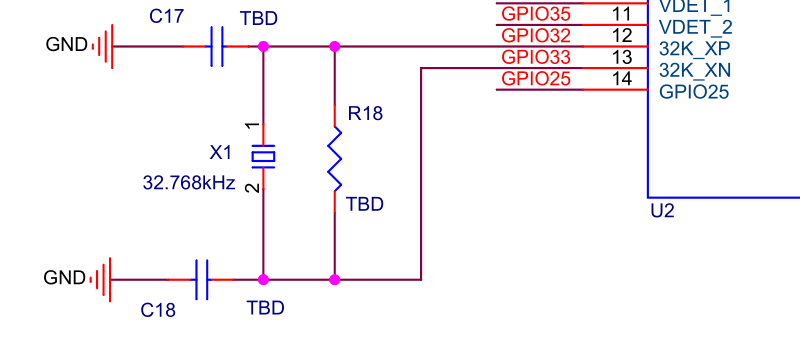

RTC Clock Source (Optional)

ESP32 supports an external 32.768 kHz crystal to act as the RTC clock. The external RTC clock source enhances timing accuracy and consequently decreases average power consumption, without impacting functionality.

Figure ESP32 Schematic for 32.768 kHz Crystal shows the schematic for the external 32.768 kHz crystal.

ESP32 Schematic for 32.768 kHz Crystal

Please note the requirements for the 32.768 kHz crystal:

Equivalent series resistance (ESR) ≤ 70 kΩ.

Load capacitance at both ends should be configured according to the crystal’s specification.

The parallel resistor R is used for biasing the crystal circuit (5 MΩ < R ≤ 10 MΩ).

For chip revisions v1.0 or v1.1, it is not recommended to use a 32.768 kHz crystal. For chip revisions v3.0 or higher, a 32.768 kHz crystal can be used, but the parallel resistor R must be installed.

When using AT firmware, the 32.768 kHz crystal is enabled by default. To prevent interference from floating crystal pins that may trigger the 32.768 kHz crystal, it is recommended to reserve grounding resistors at the 32K_XP and 32K_XN pins, but do not install them.

If the RTC clock source is not required, then the pins for the 32.768 kHz crystal can be used as GPIOs.

RF

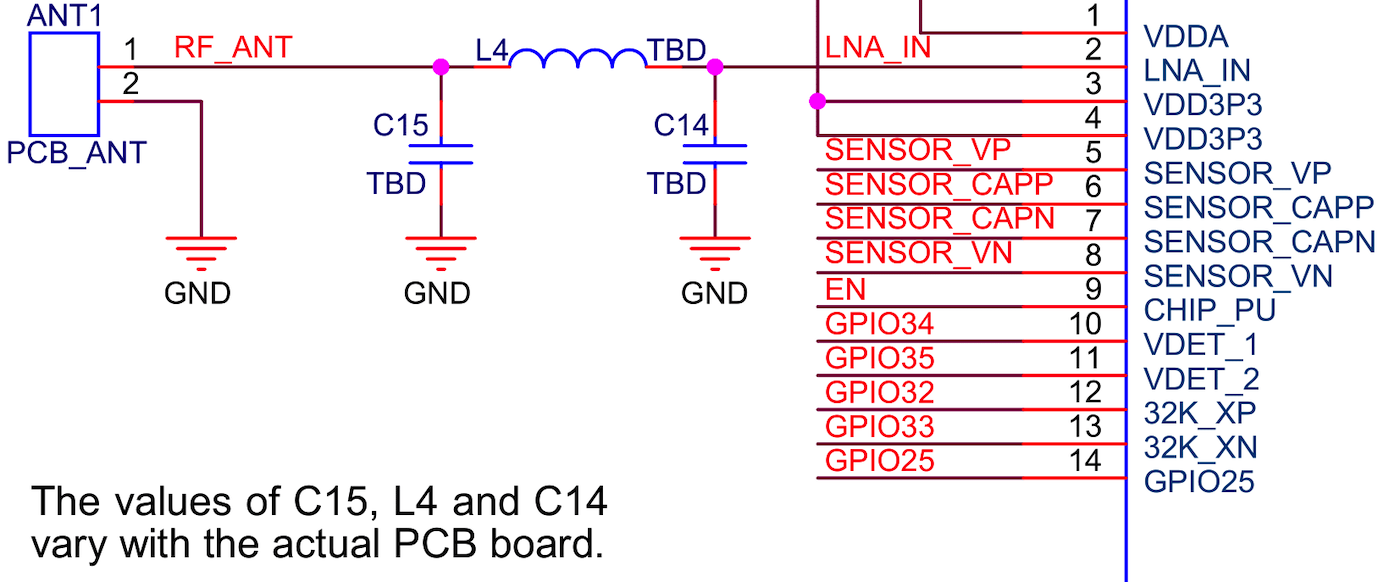

RF Circuit

ESP32’s RF circuit is mainly composed of three parts, the RF traces on the PCB board, the chip matching circuit, the antenna and the antenna matching circuit. Each part should meet the following requirements:

For the RF traces on the PCB board, 50 Ω impedance control is required.

For the chip matching circuit, it must be placed close to the chip. A CLC structure is preferred.

The CLC structure is mainly used to adjust the impedance point and suppress harmonics.

The RF matching circuit is shown in Figure ESP32 Schematic for RF Matching.

For the antenna and the antenna matching circuit, to ensure radiation performance, the antenna’s characteristic impedance must be around 50 Ω. Adding a CLC matching circuit near the antenna is recommended to adjust the antenna. However, if the available space is limited and the antenna impedance point can be guaranteed to be 50 Ω by simulation, then there is no need to add a matching circuit near the antenna.

It is recommended to include ESD protection devices for the antenna to mitigate electrostatic interference.

ESP32 Schematic for RF Matching

RF Tuning

The RF matching parameters vary with the board, so the ones used in Espressif modules could not be applied directly. Follow the instructions below to do RF tuning.

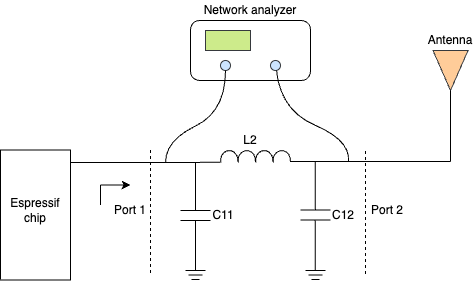

Figure ESP32 RF Tuning Diagram shows the general process of RF tuning.

ESP32 RF Tuning Diagram

In the matching circuit, define the port near the chip as Port 1 and the port near the antenna as Port 2. S11 describes the ratio of the signal power reflected back from Port 1 to the input signal power, the transmission performance is best if the matching impedance is conjugate to the chip impedance. S21 is used to describe the transmission loss of signal from Port 1 to Port 2. If S11 is close to the chip conjugate point 25+j0 and S21 is less than -35 dB at 4.8 GHz and 7.2 GHz, the matching circuit can satisfy transmission requirements.

Connect the two ends of the matching circuit to the network analyzer, and test its signal reflection parameter S11 and transmission parameter S21. Adjust the values of the components in the circuit until S11 and S21 meet the requirements. If your PCB design of the chip strictly follows the PCB design stated in Chapter PCB Layout Design, you can refer to the value ranges in Table Recommended Value Ranges for Components to debug the matching circuit.

Reference Designator |

Recommended Value Range |

Serial No. |

|---|---|---|

C11 |

1.2 ~ 1.8 pF |

GRM0335C1H1RXBA01D |

L2 |

2.4 ~ 3.0 nH |

LQP03TN2NXB02D |

C12 |

1.8 ~ 1.2 pF |

GRM0335C1H1RXBA01D |

Please use 0201 packages for RF matching components and add a stub to the first capacitor in the matching circuit at the chip end.

Note

If RF function is not required, it is recommended not to initialize the RF stack in firmware. In this case, the RF pin can be left floating. However, if RF function is enabled, make sure an antenna is connected. Operation without an antenna may result in unstable behavior or potential damage to the RF circuit.

UART

ESP32 includes to be defined UART interfaces, UART0, UART1, and UART2. U0TXD and U0RXD are GPIO1 and GPIO3 by default. Other UART signals can be mapped to any available GPIOs by software configurations.

Usually, UART0 is used as the serial port for download and log printing. For instructions on download over UART0, please refer to Section Download Guidelines. It is recommended to connect a 499 Ω series resistor to the U0TXD line to suppress harmonics.

If possible, use other UART interfaces as serial ports for communication. For these interfaces, it is suggested to add a series resistor to the TX line to suppress harmonics.

When using the AT firmware, please note that the UART GPIO is already configured (refer to Hardware Connection). It is recommended to use the default configuration.

SPI

When using the SPI function, to improve EMC performance, add a series resistor (or ferrite bead) and a capacitor to ground on the SPI_CLK trace. If space allows, it is recommended to also add a series resistor and capacitor to ground on other SPI traces. Ensure that the RC/LC components are placed close to the pins of the chip or module.

Strapping Pins

At each startup or reset, a chip requires some initial configuration parameters, such as in which boot mode to load the chip, etc. These parameters are passed over via the strapping pins. After reset, the strapping pins work as normal function pins.

GPIO0, GPIO2, GPIO5, MTDI, and MTDO are strapping pins.

All the information about strapping pins is covered in ESP32 Series Datasheet > Chapter Boot Configurations.

For strapping pin information related to VDD_SPI, please refer to Section Digital Power Supply.

In this section, we will mainly cover the strapping pins related to boot mode.

After chip reset is released, the combination of GPIO0 and GPIO2 controls the boot mode. See Table Boot Mode Control.

Boot Mode |

GPIO0 |

GPIO2 |

|---|---|---|

Default Config |

1 |

0 |

SPI Boot |

1 |

Any value |

Joint Download Boot 1 |

0 |

0 |

- 1

Joint Download Boot mode supports the following download methods:

UART Download Boot

SDIO Download Boot

Signals applied to the strapping pins should have specific setup time and hold time. For more information, see Figure Setup and Hold Times for Strapping Pins and Table Description of Timing Parameters for Strapping Pins.

Parameter |

Description |

Minimum (ms) |

|---|---|---|

tSU |

Time reserved for the power rails to stabilize before the chip enable pin (CHIP_PU) is pulled high to activate the chip. |

0 |

tH |

Time reserved for the chip to read the strapping pin values after CHIP_PU is already high and before these pins start operating as regular IO pins. |

3 |

Attention

It is recommended to place a pull-up resistor at the GPIO0 pin.

Do not add high-value capacitors at GPIO0, or the chip may enter download mode.

GPIO

The pins of ESP32 can be configured via IO MUX or GPIO matrix. IO MUX provides the default pin configurations (see ESP32 Series Datasheet > Appendix ESP32 Consolidated Pin Overview), whereas the GPIO matrix is used to route signals from peripherals to GPIO pins. For more information about IO MUX and GPIO matrix, please refer to ESP32 Technical Reference Manual > Chapter IO MUX and GPIO Matrix.

Some peripheral signals have already been routed to certain GPIO pins, while some can be routed to any available GPIO pins. For details, please refer to ESP32 Series Datasheet > Section Peripherals.

When using GPIOs, please:

Pay attention to the states of strapping pins during power-up.

Pay attention to the default configurations of the GPIOs after reset. The default configurations can be found in the table below. It is recommended to add a pull-up or pull-down resistor to pins in the high-impedance state or enable the pull-up and pull-down during software initialization to avoid extra power consumption.

Avoid using the pins already occupied by flash/PSRAM.

Note that GPIO34 and above are input-only IOs and do not have internal pull-up or pull-down resistors. If needed, please add appropriate external resistors.

Only GPIOs in the VDD3P3_RTC power domain can be controlled in Deep-sleep mode.

No. |

Name |

Power |

At Reset |

After Reset |

|---|---|---|---|---|

1 |

VDDA |

|||

2 |

LNA_IN |

VDD3P3 |

||

3 |

VDD3P3 |

|||

4 |

VDD3P3 |

|||

5 |

SENSOR_VP |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

6 |

SENSOR_CAPP |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

7 |

SENSOR_CAPN |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

8 |

SENSOR_VN |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

9 |

CHIP_PU |

VDD3P3_RTC |

||

10 |

VDET_1 |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

11 |

VDET_2 |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

12 |

32K_XP |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

13 |

32K_XN |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

14 |

GPIO25 |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

15 |

GPIO26 |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

16 |

GPIO27 |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=0 |

17 |

MTMS |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=1, wpu |

18 |

MTDI |

VDD3P3_RTC |

oe=0, ie=1, wpd |

oe=0, ie=1, wpd |

19 |

VDD3P3_RTC |

VDD3P3_RTC |

||

20 |

MTCK |

VDD3P3_RTC |

oe=0, ie=0 |

oe=0, ie=1, wpd |

21 |

MTDO |

VDD3P3_RTC |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

22 |

GPIO2 |

VDD3P3_RTC |

oe=0, ie=1, wpd |

oe=0, ie=1, wpd |

23 |

GPIO0 |

VDD3P3_RTC |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

24 |

GPIO4 |

VDD3P3_RTC |

oe=0, ie=1, wpd |

oe=0, ie=1, wpd |

25 |

GPIO16 |

VDD_SDIO |

oe=0, ie=0 |

oe=0, ie=1 |

26 |

VDD_SDIO |

|||

27 |

GPIO17 |

VDD_SDIO |

oe=0, ie=0 |

oe=0, ie=1 |

28 |

SD_DATA_2 |

VDD_SDIO |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

29 |

SD_DATA_3 |

VDD_SDIO |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

30 |

SD_CMD |

VDD_SDIO |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

31 |

SD_CLK |

VDD_SDIO |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

32 |

SD_DATA_0 |

VDD_SDIO |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

33 |

SD_DATA_1 |

VDD_SDIO |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

34 |

GPIO5 |

VDD3P3_CPU |

oe=0, ie=1, wpd |

oe=0, ie=1, wpd |

35 |

GPIO18 |

VDD3P3_CPU |

oe=0, ie=0 |

oe=0, ie=1 |

36 |

GPIO23 |

VDD3P3_CPU |

oe=0, ie=0 |

oe=0, ie=1 |

37 |

VDD3P3_CPU |

|||

38 |

GPIO19 |

VDD3P3_CPU |

oe=0, ie=0 |

oe=0, ie=1 |

39 |

GPIO22 |

VDD3P3_CPU |

oe=0, ie=0 |

oe=0, ie=1 |

40 |

U0RXD |

VDD3P3_CPU |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

41 |

U0TXD |

VDD3P3_CPU |

oe=0, ie=1, wpu |

oe=0, ie=1, wpu |

42 |

GPIO21 |

VDD3P3_CPU |

oe=0, ie=0 |

oe=0, ie=1 |

43 |

VDDA |

|||

44 |

XTAL_N |

VDDA |

||

45 |

XTAL_P |

VDDA |

||

46 |

VDDA |

|||

47 |

CAP2 |

VDDA |

||

48 |

CAP1 |

VDDA |

ie – input enable

oe – output enable

wpu – internal weak pull-up resistor enable

wpd – internal weak pull-down resistor enable

ADC

Table below shows the correspondence between ADC channels and GPIOs.

GPIO Pin Name |

ADC Function |

|---|---|

SENSOR_VP |

ADC1_CH0 |

SENSOR_CAPP |

ADC1_CH1 |

SENSOR_CAPN |

ADC1_CH2 |

SENSOR_VN |

ADC1_CH3 |

32K_XP |

ADC1_CH4 |

32K_XN |

ADC1_CH5 |

VDET_1 |

ADC1_CH6 |

VDET_2 |

ADC1_CH7 |

GPIO4 |

ADC2_CH0 |

GPIO0 |

ADC2_CH1 |

GPIO2 |

ADC2_CH2 |

MTDO |

ADC2_CH3 |

MTCK |

ADC2_CH4 |

MTDI |

ADC2_CH5 |

MTMS |

ADC2_CH6 |

GPIO27 |

ADC2_CH7 |

GPIO25 |

ADC2_CH8 |

GPIO26 |

ADC2_CH9 |

Please add a 0.1 μF filter capacitor between ESP pins and ground when using the ADC function to improve accuracy.

When RTC peripherals (SAR ADC1/SAR ADC2/AMP) is powered on, the inputs of GPIO36 (SENSOR_VP) and GPIO39 (SENSOR_VN) will be pulled down for approximately 80 ns. If SENSOR_VP and SENSOR_VN are used as GPIOs in the design, while ADC is supported by other pins, then software should disregard the glitch. Optionally, use SENSOR_VP and SENSOR_VN as ADC pins.

ADC1 is recommended over ADC2 as the latter cannot be used when Wi-Fi function is enabled.

The calibrated ADC results after hardware calibration and software calibration are shown in the list below. For higher accuracy, you may implement your own calibration methods.

When ATTEN=0 and the effective measurement range is 100 ~ 950 mV, the total error is ±23 mV.

When ATTEN=1 and the effective measurement range is 100 ~ 1250 mV, the total error is ±30 mV.

When ATTEN=2 and the effective measurement range is 150 ~ 1750 mV, the total error is ±40 mV.

When ATTEN=3 and the effective measurement range is 150 ~ 2450 mV, the total error is ±60 mV.

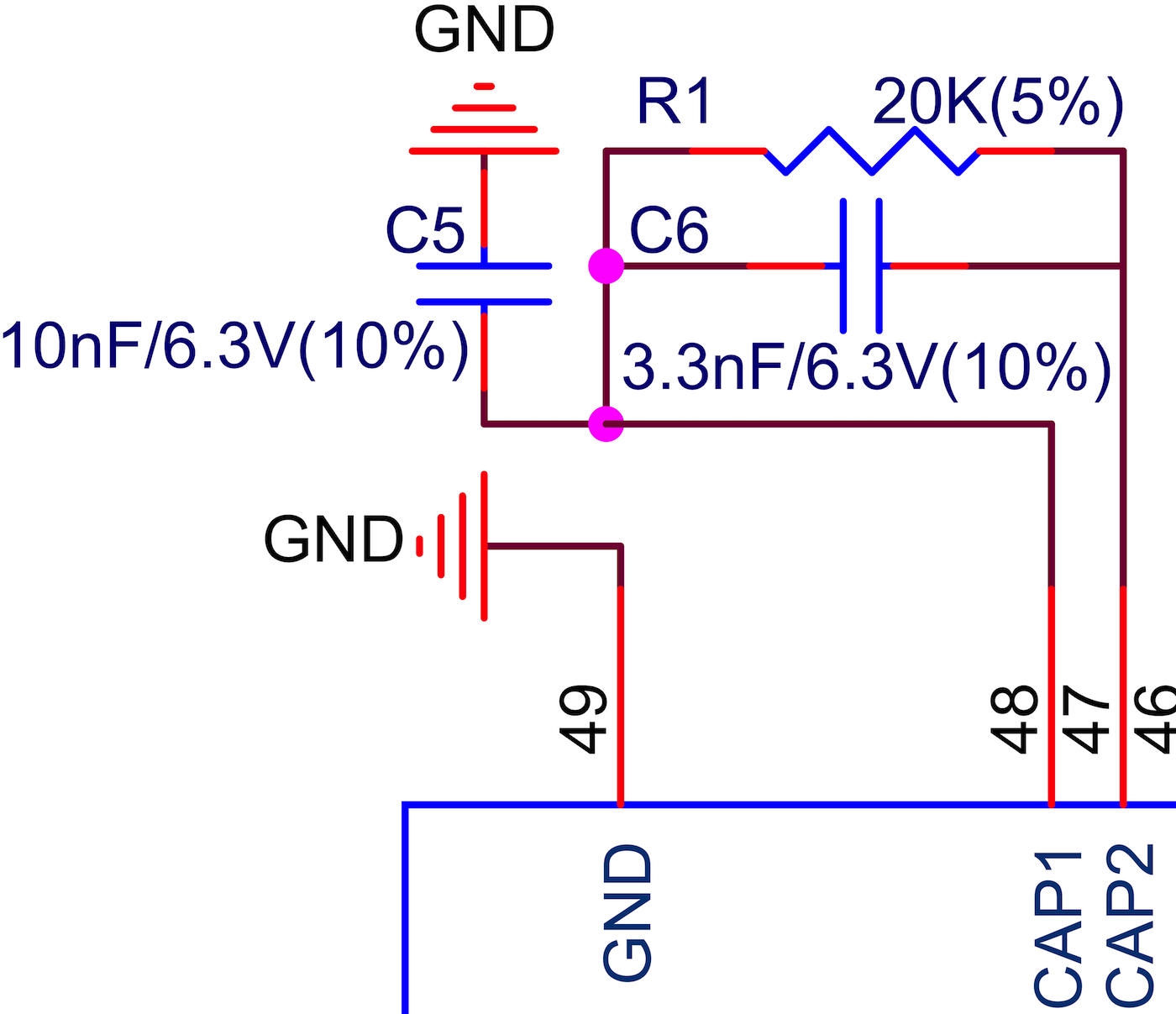

External Capacitor

Figure ESP32 Schematic for External Capacitor shows the schematic of components connected to pin47 CAP2 and pin48 CAP1.

C5 (10 nF) that connects to CAP1 should be of 10% tolerance and is required for proper operation of ESP32.

RC circuit between CAP1 and CAP2 pins may be omitted under certain conditions. This circuit is used when entering Deep-sleep mode. During this process, to minimize power consumption, the voltage to power ESP32 internals is dropped from 1.1 V to around 0.7 V. The RC circuit is used to minimize the period of the voltage drop. If removed, this process will take longer and the power consumption in Deep-sleep will be higher. If particular application of ESP32 is not using Deep-sleep mode, or power consumption is less critical, then this circuit is not required.

ESP32 Schematic for External Capacitor

SDIO

ESP32 supports an SD/SDIO/MMC host controller and an SD/SPI slave controller, compliant with the SDIO 2.0 specification. For the SDIO host/slave controller, ESP32 provides two sets of slot GPIOs for use. Since the GPIOs in slot0 are by default connected to flash, please connect the GPIOs and signal lines according to slot1 as shown in Table SDIO Pin Configuration.

CMD |

CLK |

DAT0 |

DAT1 |

DAT2 |

DAT3 |

Note |

|

|---|---|---|---|---|---|---|---|

Slot0 |

GPIO11 |

GPIO6 |

GPIO7 |

GPIO8 |

GPIO9 |

GPIO10 |

Used to connect flash by default. Not recommended for other use. |

Slot1 |

GPIO15 |

GPIO14 |

GPIO2 |

GPIO4 |

GPIO12 |

GPIO13 |

Multiplexed with JTAG, touch, EMAC, and strapping functions. |

When connecting GPIOs in slot1 to signal lines, please note:

When ESP32 works as an SDIO host, it is recommended to add pull-up resistors on the used pins. Unused pins can be utilized for other purposes.

When ESP32 works as an SDIO slave, add pull-up resistors on all pins, regardless of whether these pins are used for SDIO or not. Unused pins cannot be used for other purposes.

Since there are strapping pins among the SDIO GPIOs, enabling pull-up resistors for SDIO may cause some conflicts. For specific solutions, please refer to SD Pull-up Requirements.

For more information on SDIO configuration, please refer to API References.

Touch Sensor

ESP32 has 10 capacitive-sensing GPIOs, which detect variations induced by touching or approaching the GPIOs with a finger or other objects. The low-noise nature of the design and the high sensitivity of the circuit allow relatively small pads to be used. Arrays of pads can also be used, so that a larger area or more points can be detected.

Table below shows the correspondence between touch sensor channels and GPIOs.

GPIO Pin Name |

Touch Sensor Function |

|---|---|

GPIO4 |

TOUCH00 |

GPIO0 |

TOUCH1 |

GPIO2 |

TOUCH2 |

MTDO |

TOUCH3 |

MTCK |

TOUCH4 |

MTDI |

TOUCH5 |

MTMS |

TOUCH6 |

GPIO27 |

TOUCH7 |

32K_XN |

TOUCH8 |

32K_XP |

TOUCH9 |

When using the touch function, it is recommended to populate a series resistor at the chip side to reduce the coupling noise and interference on the line, and to strengthen the ESD protection. The recommended resistance is from 470 Ω to 2 kΩ, preferably 510 Ω. The specific value depends on the actual test results of the product.

Ethernet MAC

ESP32 provides a media access control (MAC) interface that complies with the IEEE-802.3-2008 standard for Ethernet communication. The ESP32-Ethernet-Kit board only supports the Reduced Media-Independent Interface (RMII). The allocation of the ESP32 pins to the RMII interface is shown in the table below.

Pin Name |

Function 6 |

RMII (int_osc) |

RMII (ext_osc) |

|---|---|---|---|

GPIO0 |

EMAC_TX_CLK |

CLK_OUT(O) |

EXT_OSC_CLK(I) |

GPIO21 |

EMAC_TX_EN |

TX_EN(O) |

TX_EN(O) |

GPIO19 |

EMAC_TXD0 |

TXD[0](O) |

TXD[0](O) |

GPIO22 |

EMAC_TXD1 |

TXD[1](O) |

TXD[1](O) |

GPIO27 |

EMAC_RX_DV |

CRS_DV(I) |

CRS_DV(I) |

GPIO25 |

EMAC_RXD0 |

RXD[0](I) |

RXD[0](I) |

GPIO26 |

EMAC_RXD1 |

RXD[1](I) |

RXD[1](I) |

GPIO16 |

EMAC_CLK_OUT |

CLK_OUT(O) |

– |

GPIO17 |

EMAC_CLK_OUT_180 |

CLK_OUT_180(O) |

– |

Any GPIO |

– |

MDC(O) |

MDC(O) |

Any GPIO |

– |

MDIO(IO) |

MDIO(IO) |

For an Ethernet solution, it is recommended to use GPIO0 as the clock input. Be aware that GPIO0 also acts as a strapping pin and it can be affected by the clock during chip power-up and may enter download mode as a result. Therefore, make sure you have turned off the clock output on the PHY side before powering up the chip. The ESP32-Ethernet-Kit board uses GPIO to control PHY’s reset pin and turn off the clock output. However, not all PHYs support this design, so it is crucial to verify functionality during testing. If this design cannot be implemented, consider alternative methods to ensure that GPIO0 remains unaffected during power-up. For a reference design please see ESP32-Ethernet-Kit User Guide.

If you need to use Wi-Fi and Ethernet simultaneously, do not use the internal APLL clock to generate the RMII clock, as this can lead to clock instability. Instead, use the RMII clock from the PHY side or an external clock source. For further details, please refer to ESP32-Ethernet-Kit User Guide > RMII Clock Selection.