PCB 版图布局

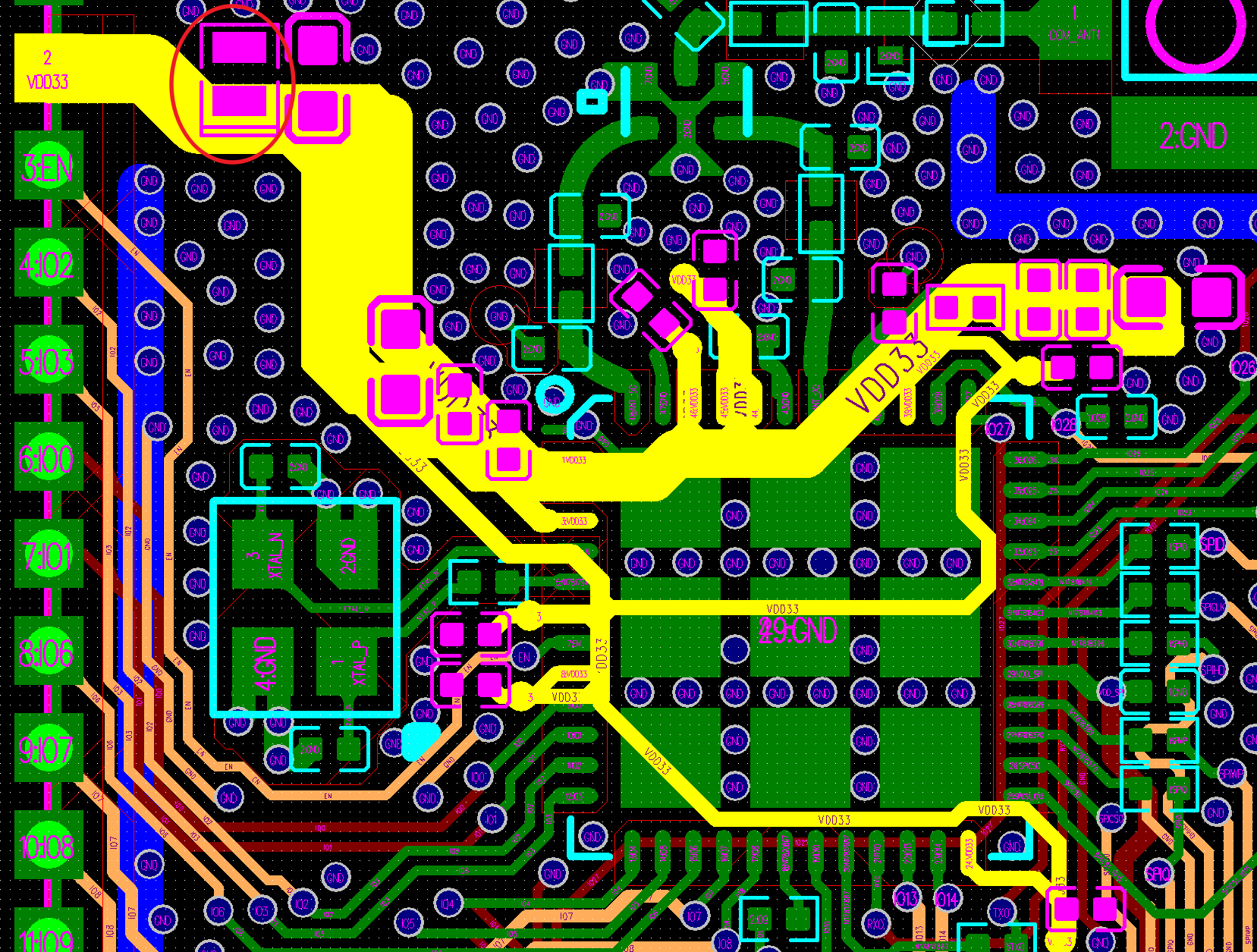

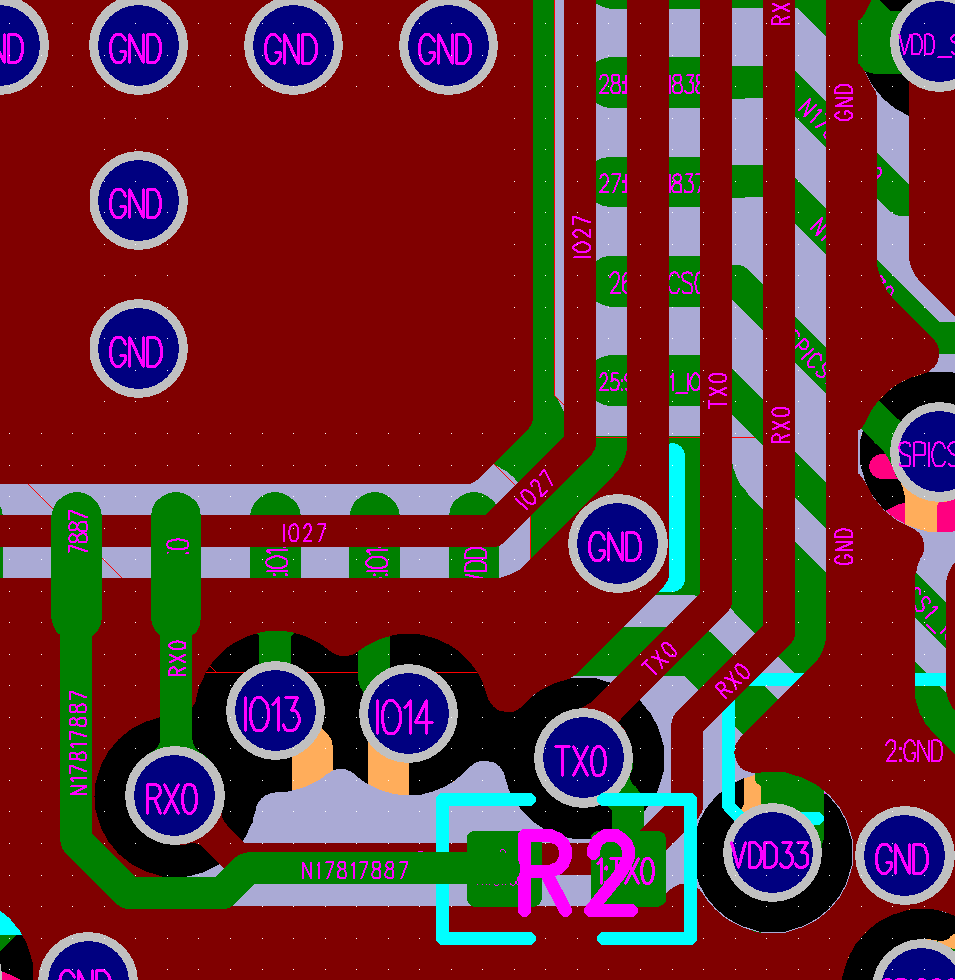

本章节将以 ESP32-C5 模组的 PCB 布局为例(见图 ESP32-C5 模组版图参考设计),介绍 ESP32-C5 系列芯片的 PCB 布局设计要点。

ESP32-C5 模组版图参考设计

基于芯片的版图设计通用要点

建议采用四层板设计,即:

第一层(顶层),主要用于走信号线和摆件。

第二层(地层),不走信号线,保证一个完整的地平面。

第三层(电源线层),铺地平面,使射频及晶振部分可以得到更好的屏蔽。在保证射频及晶振部分下方完整地平面的情况下,将电源走在该层,可适度走信号线。

第四层(底层),不建议摆件,可适度走信号线。

电源

四层板设计

图 ESP32-C5 系列芯片四层板电源设计 所示为四层板设计的电源走线。

ESP32-C5 系列芯片四层板电源设计

推荐优先采用四层板设计。电源走线请尽量走在内层(非地层),通过过孔连接至芯片管脚处。主干电源换层处请至少保证两个过孔。其余电源走线上的钻孔的直径应不小于电源走线的宽度。

图 ESP32-C5 系列芯片四层板电源设计 中黄色高亮信号线即为 3.3 V 电源走线。主干电源走线的线宽建议至少 30 mil。模拟电源 管脚 1、3、40 和 41 处的 VDDA6、VDDA7、VDDA1 和 VDDA2 分支走线建议至少 20 mil。其他分支电源走线建议 10 mil。电源走线周围注意包地良好。

图 ESP32-C5 系列芯片四层板电源设计 中红色圆圈标示的是 ESD 保护管,需靠近电源端口放置。电源走线进入芯片前需添加一个 10 μF 电容。而后电源走线可在此分支,进行星形走线,减少不同电源管脚之间的耦合。尤其注意 2.4 GHz 和 5 GHz 电源走线需要分开。

管脚 1、3、40 和 41 处电源因为是射频相关电源,请在管脚上各添加一个 10 µF 电容,并在管脚 1、3 处再各放置一个电容。

请靠近管脚 40、41 添加 CLC/LC 滤波电路用于抑制高频谐波。该电源可以考虑 45 度出线的方式,拉开和旁边射频走线之间的距离。除了 10 uF 电容,其余器件推荐使用 0201 封装,这样可以把管脚 2、3 的滤波电路放的更靠近管脚,能够和周围的射频、GPIO 之间添加 GND 隔离,并尽量能放置地孔。使用了 0201 封装,可以在靠近芯片的第一个电容上加一段枝节到底层,其余层做 keep-out 隔离处理,可以进一步抑制谐波干扰,详见下图。

ESP32-C5 系列管脚 40、41 电源设计

图 ESP32-C5 系列芯片四层板电源设计 中,因为 管脚 1、3、40 和 41 处的 VDDA6、VDDA7、VDDA1 和 VDDA2 模拟电源和芯片电源入口接近,因此只使用了一个 10 μF 电容。如果芯片电源入口不靠近 管脚 1、3、40 和 41 处的 VDDA6、VDDA7、VDDA1 和 VDDA2,请在芯片电源入口处和 管脚 1、3、40 和 41 处的 VDDA6、VDDA7、VDDA1 和 VDDA2 处都添加一个 10 μF 电容。

其他每个电源管脚上请放置合适的去耦电容。去耦电容的接地管脚请靠近打地孔,保证较短的返回路径。

芯片下方的地焊盘需要至少打九个地孔连接到地平面。

芯片及其外围电路的器件地焊盘,建议和地铺铜充分接触,不要用走线连接。

如图 ESP32-C5 系列芯片四层板电源设计 所示,如需在模组背面添加散热焊盘 EPAD,建议采用多宫格设计,间隙处盖防焊油墨,地孔打在间隙处。这样可以有效改善模组 EPAD 焊接至底板时的漏锡问题。

建议把 EPAD 通过一定宽度的走线或者铜皮连接至外部的大面积铺地上,详见下图。

ESP32-C5 系列芯片底部 EPAD 设计

晶振

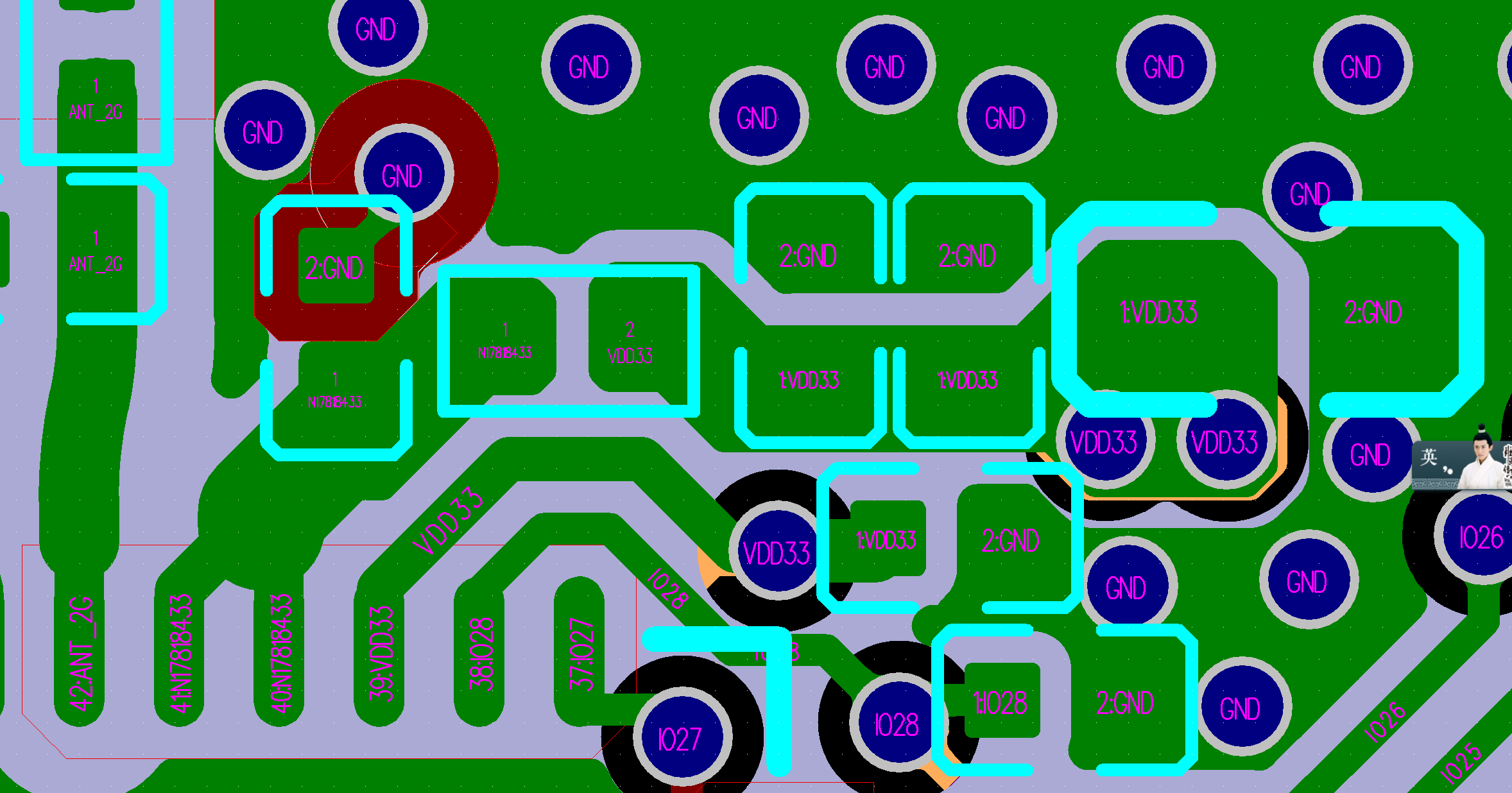

图 ESP32-C5 系列芯片晶振设计(顶层有 keep-out) 为晶振通过通孔连接到地平面,但是顶层通过设置 keep-out 和地隔离开的参考设计图。

ESP32-C5 系列芯片晶振设计(顶层有 keep-out)

如果顶层的地很充分,建议顶层设置 keep-out 和地隔离开,既可以减小寄生电容,也可以抑制温度传导,以防影响频偏。如果不充分,建议不设置 keep-out,和地充分接触。

晶振设计应遵循以下规范:

需要保证射频、晶振和芯片有一个完整的地平面。

晶振需离芯片时钟管脚稍远一些放置,防止晶振干扰到芯片。间距应至少为 2.4 mm。同时晶振走线须用地包起来,周围用密集的地孔屏蔽隔离。

晶振的时钟走线不可打孔走线。

晶振上的串联元器件请靠近芯片放置。

晶振外接的对地调节电容请靠近晶振左右两侧摆放,不可直接连接在串联元器件上。电容尽量置于时钟走线连接末端,保证电容的地焊盘靠近晶振的地焊盘放置。

晶振下方都不能走高频数字信号,最好是晶振下方不走任何信号线。晶振时钟走线两侧的电源线上的过孔应尽可能地远离时钟走线放置,并使时钟走线两侧尽可能包地。

晶振为敏感器件,晶振周围不能放置磁感应器件,比如大电感等,保证晶振周围有干净的大面积地平面。

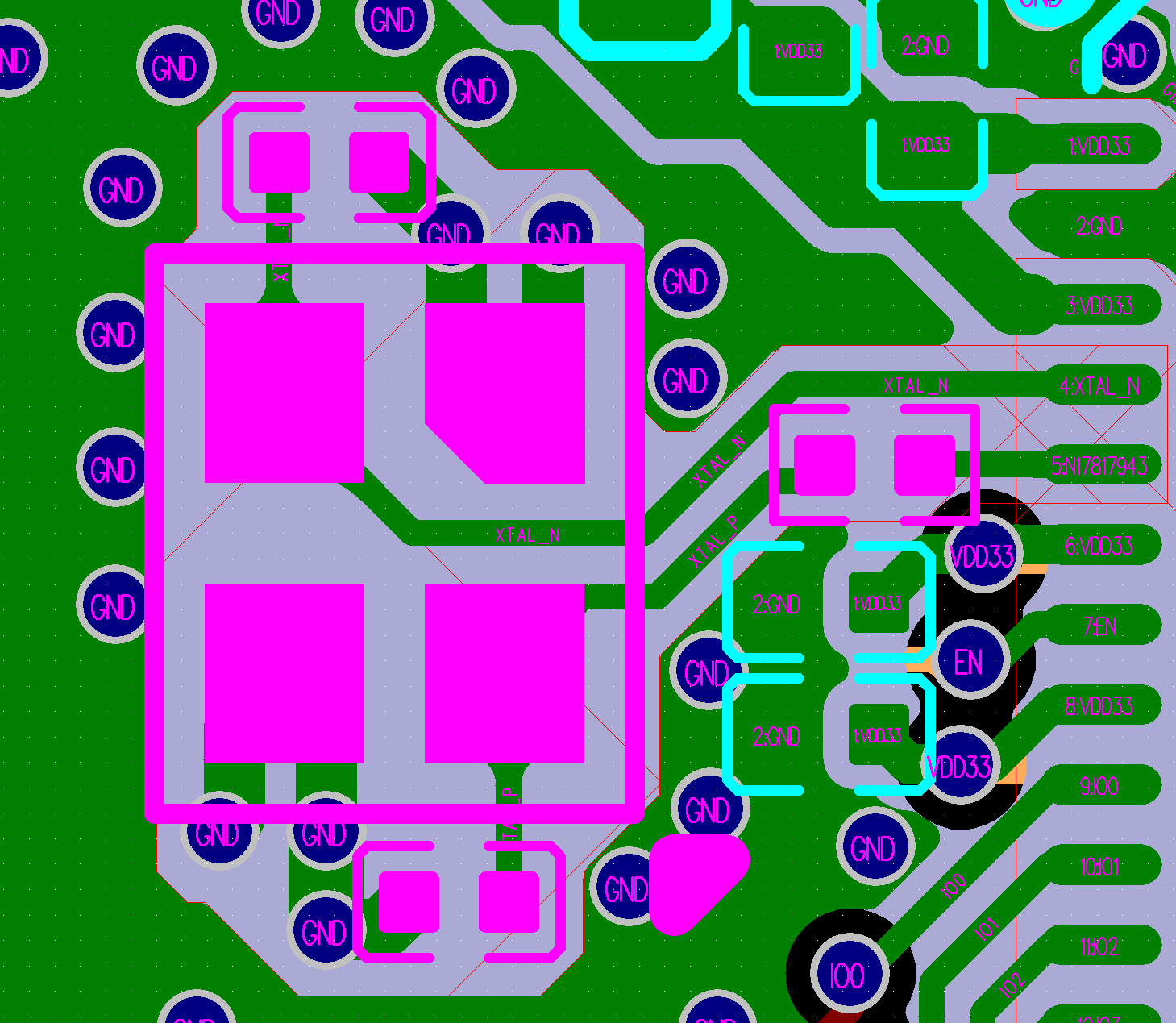

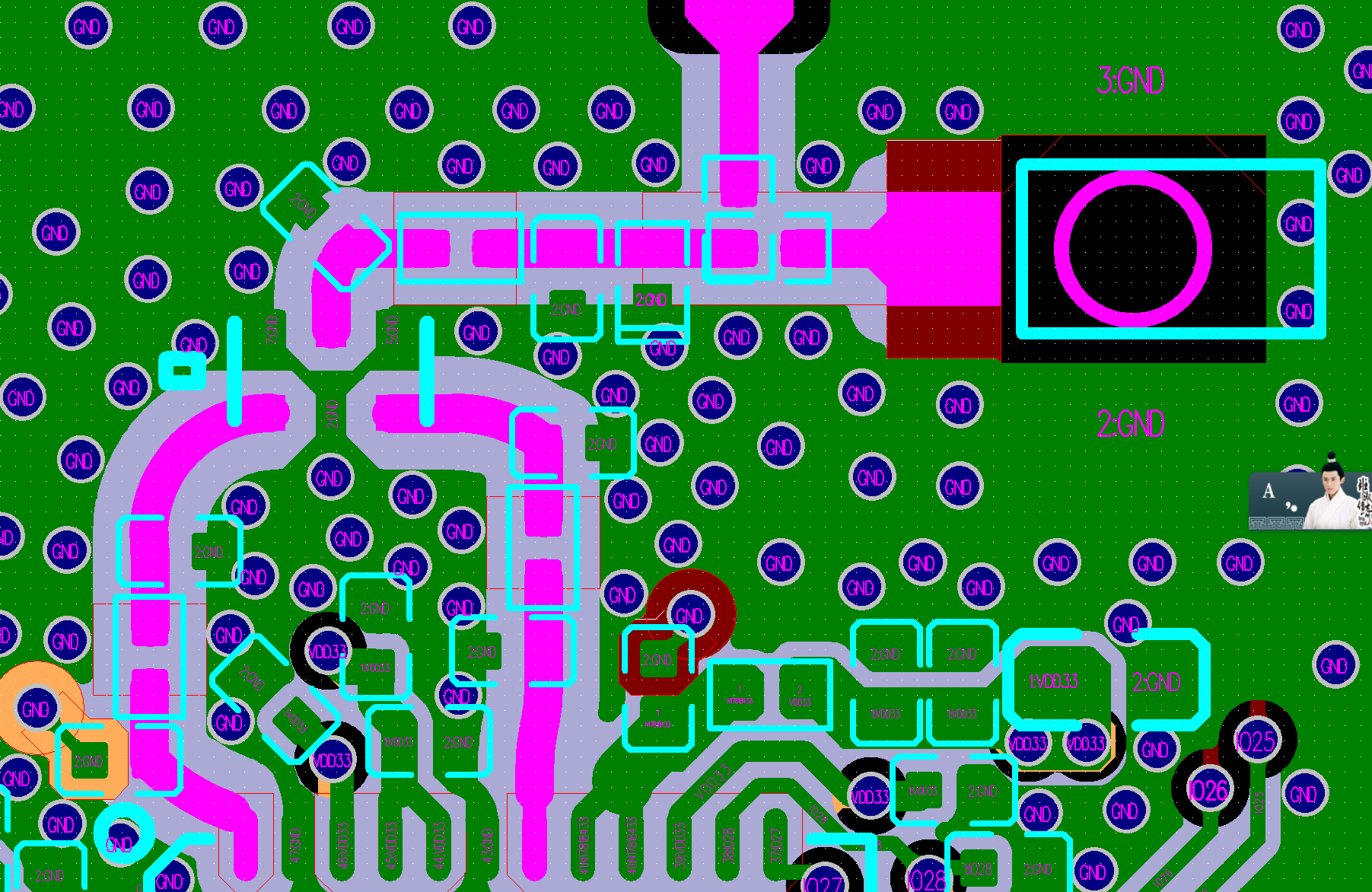

射频

图 ESP32-C5 系列芯片四层板射频部分版图设计 中粉色高亮走线即为射频走线。

ESP32-C5 系列芯片四层板射频部分版图设计

射频版图设计应遵循以下规范:

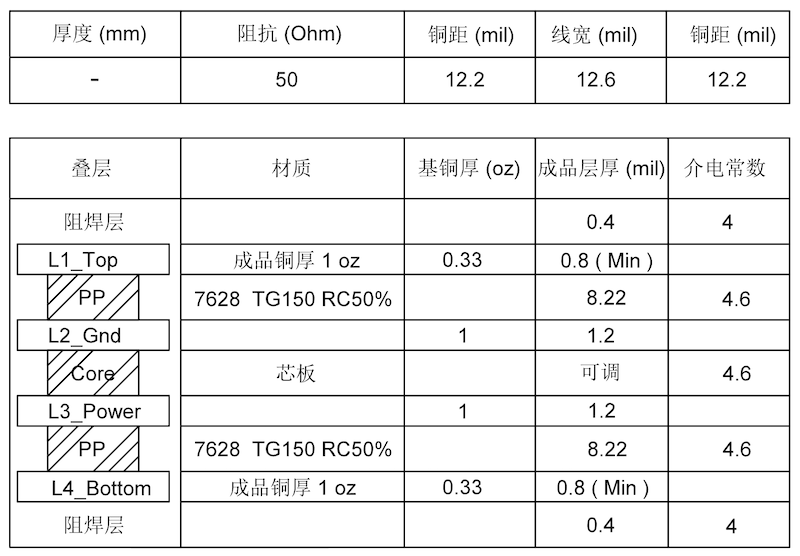

射频走线需做 50 Ω 阻抗控制,参考平面为芯片邻层。射频走线在做 50 Ω 阻抗控制时,可参考下图所示的 PCB 叠层结构设计。

ESP32-C5 系列芯片 PCB 叠层结构设计

调节芯片需要至少一个 CLC 匹配电路。请使用 0201 器件,把匹配器件靠近管脚放置,并呈 Z 字型摆放。也就是说两个电容勿朝同一方向,以减少互相干扰。

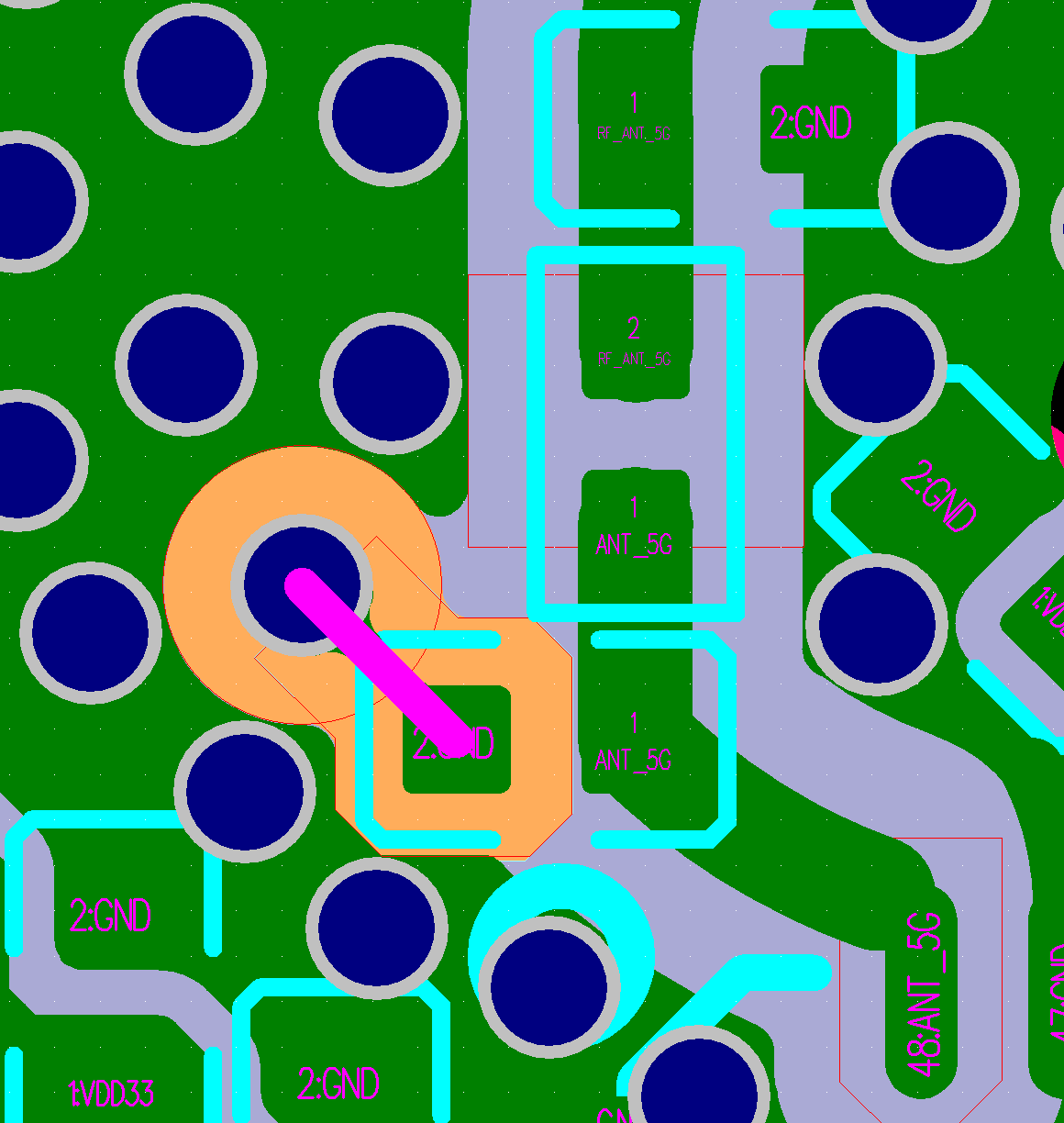

5G 射频接口的 CLC 匹配电路中靠近芯片侧的对地电容上请添加一段枝节,以有效抑制二次谐波。枝节的长度建议为 10 mil,线宽根据 PCB 叠层结构进行确定,确保枝节的特征阻抗为 100 Ω ± 10%。此外,枝节地孔与第三层相连,第一、二层做 keep-out 隔离处理。下图 ESP32-C5 系列芯片四层板射频枝节设计 中的高亮走线即为枝节。当 5G 射频接口的 CLC 匹配电路元器件封装为 0402 或者更大时,则无需做枝节处理。

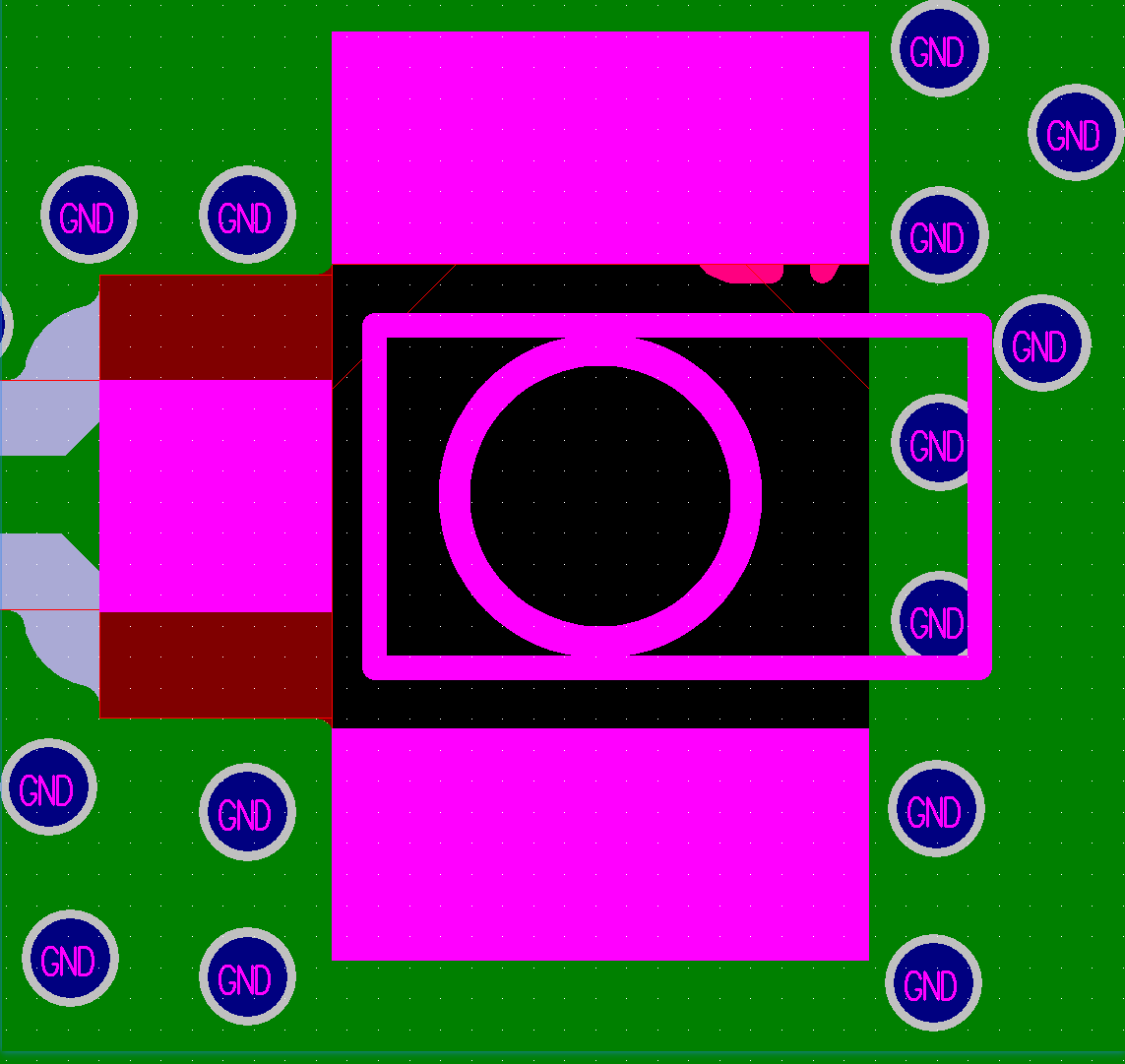

IPEX 天线连接器下方建议全部层净空,详见图 ESP32-C5 系列芯片 IPEX 版图设计。

PCB 天线请注意需要经过仿真和实际开发板测试。建议额外增加一组 CLC 匹配电路用于调节天线,该电路需尽可能地靠近天线端。

ESP32-C5 系列芯片四层板射频枝节设计

ESP32-C5 系列芯片 IPEX 版图设计

射频走线线宽请注意保持一致,不可有分支走线。射频走线长度须尽量短,并注意周围密集地孔屏蔽。

射频走线在表层,走线不可有过孔,即不能跨层走线,且尽量使用 135° 角走线或是圆弧走线。

射频走线须保证相邻层完整地平面,射频走线下方尽可能不要有任何走线。

射频走线附近不能有高频信号线。射频上的天线必须远离所有传输高频信号的器件,比如晶振、DDR SDRAM、高频时钟等。另外,USB 端口、USB 转串口信号的芯片、UART 信号线(包括走线、过孔、测试点、插针引脚等)都必须尽可能地远离天线。且 UART 信号线做包地处理,周围加地孔屏蔽。

Flash 及 PSRAM

Flash 及 PSRAM 的设计应遵循以下规范:

SPI 通信线上预留的 0 Ω 串联电阻请靠近 ESP32-C5 侧放置。

SPI 走线请尽可能地走到内层(例如第三层),并且时钟及数据走线都单独进行包地处理。

如果 flash 和 PSRAM 距离 ESP32-C5 较远,建议在 VDD_SPI 电源、flash 和 PSRAM 电源处都放置合适的去耦电容。

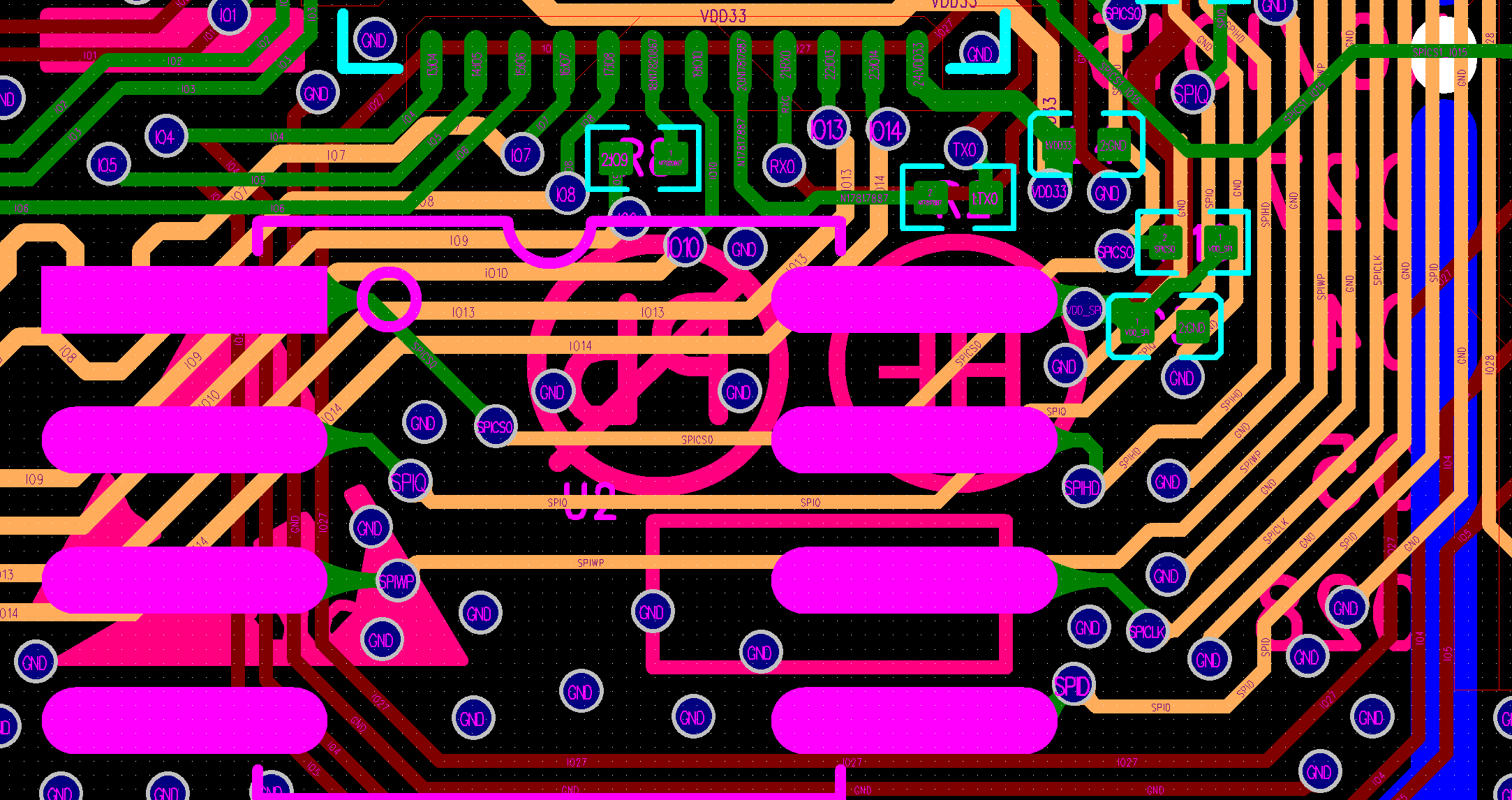

图 ESP32-C5 系列芯片 Quad SPI Flash 版图设计 所示为 quad flash 版图设计。

ESP32-C5 系列芯片 Quad SPI Flash 版图设计

UART

图 ESP32-C5 系列芯片 UART 版图设计 所示为 UART 版图设计。

ESP32-C5 系列芯片 UART 版图设计

UART 版图设计应遵循以下规范:

U0TXD 线上的串联电阻请靠近芯片侧并远离晶振放置。

U0TXD、U0RXD 在顶层的走线需尽量短。

UART 走线两侧请注意包地处理,周围加地孔屏蔽。

基于模组的版图设计通用要点(模组在底板上的位置摆放)

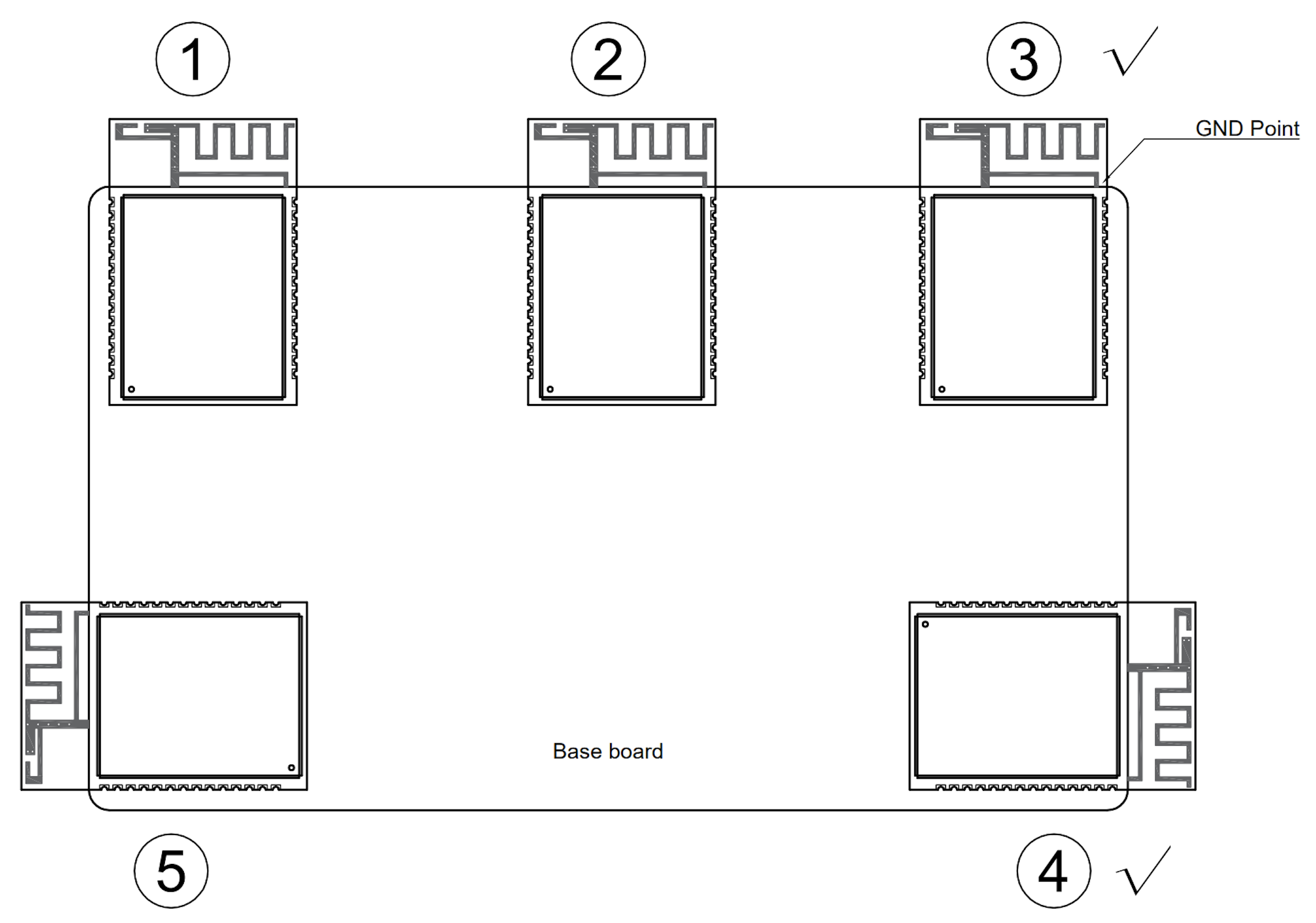

如使用模组进行板上 (on-board) 设计,需注意模组在底板的布局,应尽可能地减小底板对模组 PCB 天线性能的影响。

建议将模组天线区域伸出板边,接地点 靠近底板板边放置。在下面模组摆放位置图中,✓ 代表强烈推荐的摆放位置,其他位置不推荐。

ESP32-C5 系列模组 (天线接地点在右侧) 在底板上的位置示意图

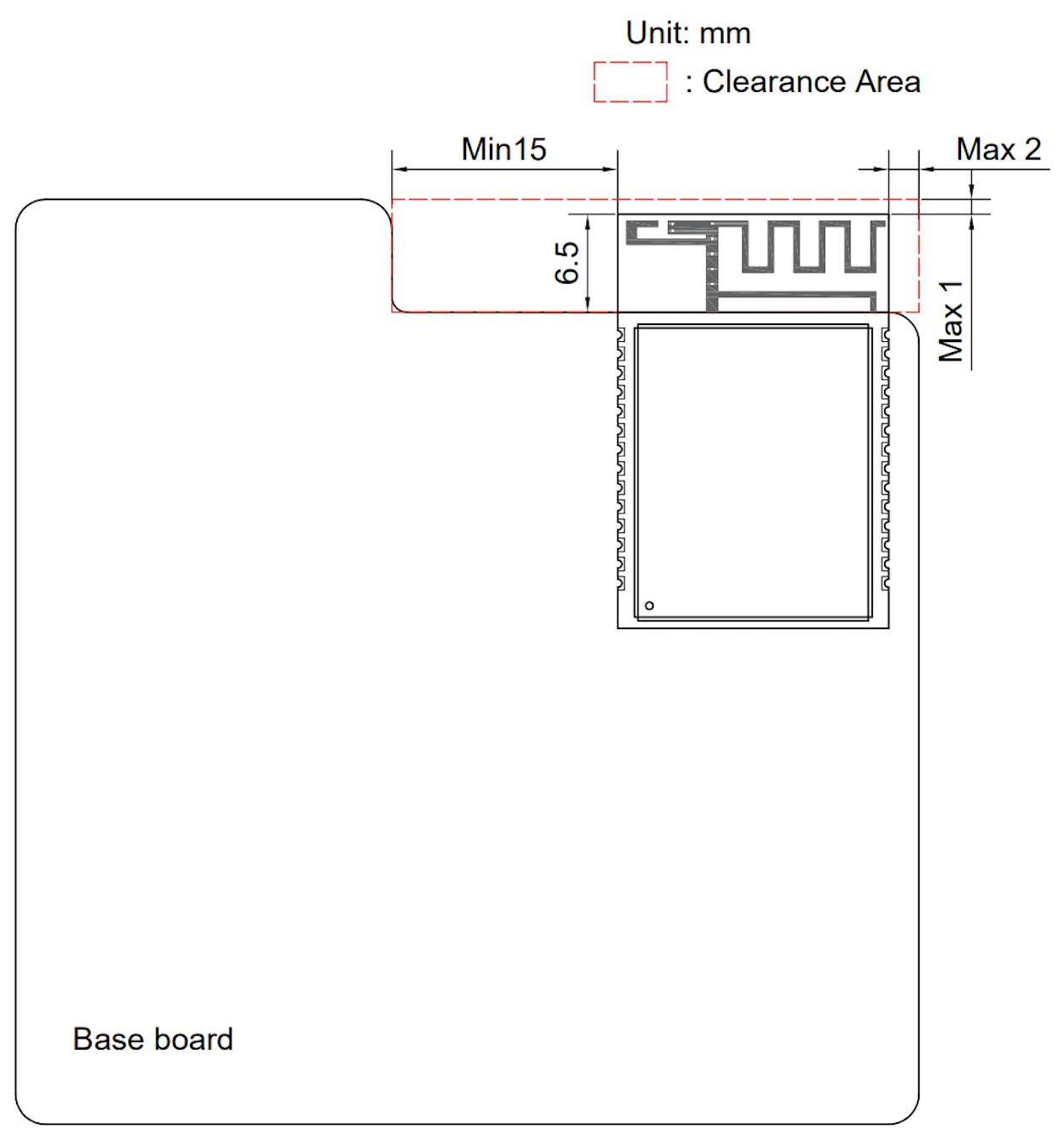

如果天线无法伸出板边,请保证给 PCB 天线一个足够大的净空区域(严禁铺铜、走线、摆放元件),该净空区域建议至少 15 mm(所有方向上都是)。PCB 天线下方区域的底板请切割掉,以尽可能地减少底板板材对 PCB 天线的影响。接地点 尽量靠近板边放置。图 ESP32-C5 天线区域净空示意图 以 接地点 在 右侧 的模组为例,画出了建议的净空区。

ESP32-C5 天线区域净空示意图

涉及整机设计时,请注意考虑外壳对天线的影响,并进行 RF 验证。请注意最终仍需要对整机产品进行吞吐量和通讯距离等测试来确保产品射频性能。

USB

USB 版图设计应遵循以下规范:

USB 线上预留的电阻和电容请靠近芯片侧放置。

USB 走线请按照差分走线,差分线阻抗控制标准是 90 Ω,误差不能大于 ±10%,保持平行等长。

USB 差分走线尽可能减少打孔换层,从而可以更好的做到阻抗的控制,避免信号的反射。如果必须打孔,请在每次打孔换层的地方加一对地孔回流。

USB 走线下方一定要有参考层(推荐用地层),且一定要保证参考层的连续性。

USB 走线两侧请注意包地处理。

SDIO

SDIO 版图设计应遵循以下规范:

SDIO 走线因为速率较高,需要尽量控制其寄生电容。

SDIO_CMD、SDIO_DATA0 ~ SDIO_DATA3 走线长度以 SDIO_CLK 走线长度为基准 ± 50 mil,需要时绕蛇形线。

SDIO 走线请保证 50 Ω 单端阻抗控制,误差不能大于 ±10%。

从芯片 SDIO 管脚到对端 SDIO 接口的总长度越短越好,最好在 2000 mil 以内。

SDIO 走线要保证不跨平面。SDIO 走线下方一定要有要有参考层(推荐用地层),且一定要保证参考层的连续性。

SDIO_CLK 走线两侧请注意包地处理。

备注

芯片版本 v1.0 支持该外设,v0.1 暂不可用。

版图设计常见问题

为什么芯片发包时,电源纹波很小,但射频的 TX 性能不好?

现象分析: 射频的 TX 性能不仅受电源纹波的影响,还受到晶振的影响。晶振的本身质量不好,频偏过大会影响射频的 TX 性能。或者晶振受到高频信号干扰,比如晶振的输入输出信号线走线跨层交叉,使得晶振的输入信号耦合到输出信号上,输出信号耦合到输入信号上,也会影响射频的 TX 性能。另外,如果晶振的下方有其他高频信号走线,比如 SDIO 走线、UART 走线,也会导致晶振无法正常工作。最后,晶振旁边有感性器件或辐射器件,比如大电感、天线等也会导致芯片的射频性能不好。

解决方法: 此问题主要是在布局上,可以重新布局,详见章节 晶振。

为什么芯片发包时,仪器测试到的 power 值比 target power 值要高很多或者低很多,且 EVM 比较差?

现象分析: 仪器检测到的 power 值与 target power 相差较大,可能是由于芯片射频管脚输出到天线这一段传输线上阻抗不匹配导致信号在传输过程中有反射。其次,阻抗不匹配会影响到芯片内部 PA 的工作状态,使得 PA 非正常过早进入饱和区域,继而使得信号失真度高,EVM 自然会变差。

解决方法: 射频走线上预留了一个 π 型电路,可以根据需求对天线进行阻抗匹配,使得从芯片射频管脚往天线端看去,阻抗接近芯片端口阻抗。