原理图设计

概述

ESP32-S2 系列芯片的核心电路只需要 20 个左右的电阻电容电感和 1 个无源晶振,以及 1 个 SPI flash。为了能够更好地保证 ESP32-S2 系列芯片的工作性能,本章将详细介绍 ESP32-S2 系列芯片的原理图设计。

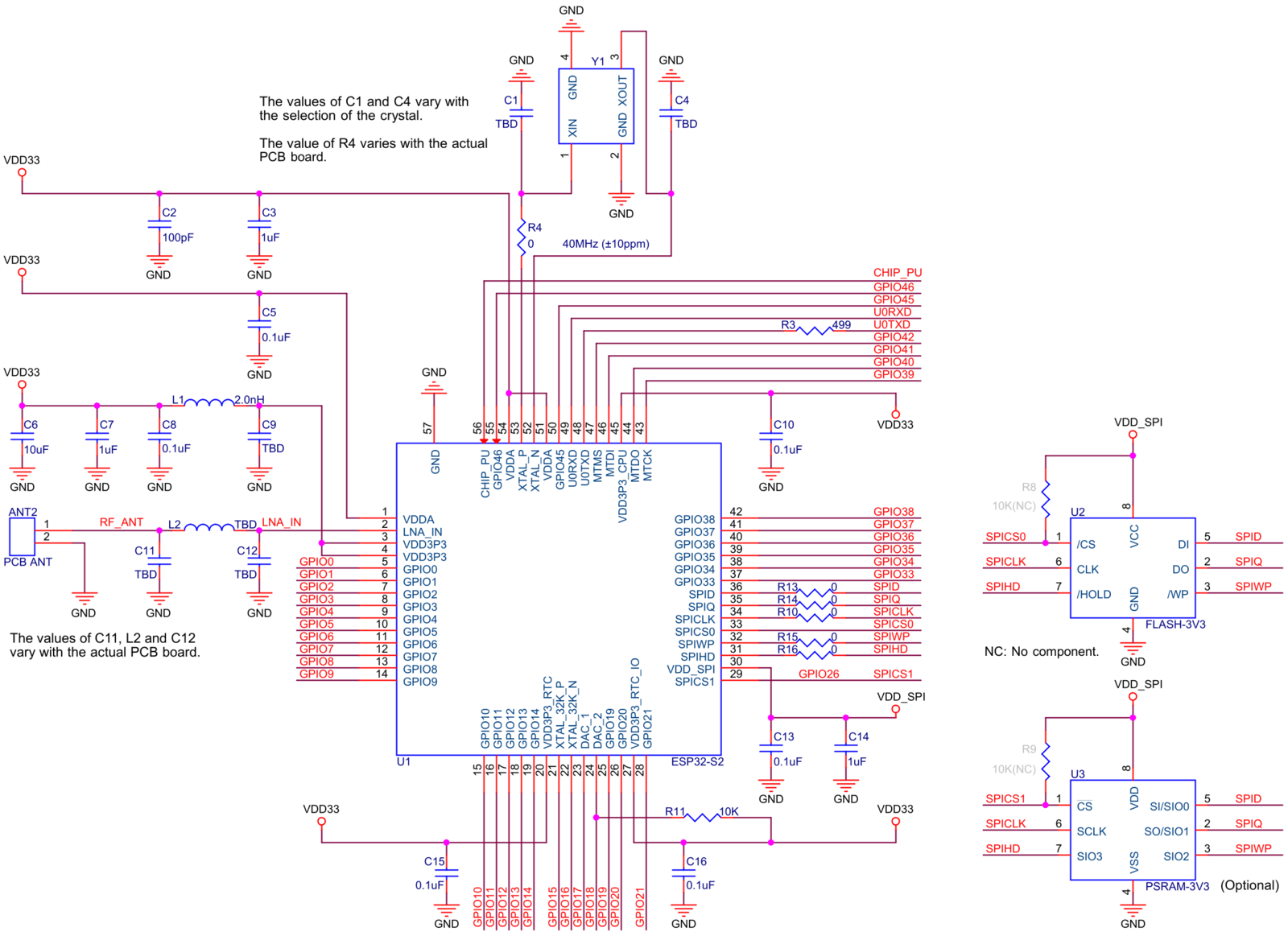

下图所示为 ESP32-S2 的核心电路参考设计,您可以将它作为您的原理图设计的基础。

ESP32-S2 系列芯片参考设计原理图

ESP32-S2 系列芯片的核心电路图的设计有以下重要组成部分:

下文将分别对这些部分进行描述。

电源

电源电路设计的通用要点有:

使用单电源供电时,建议供给 ESP32-S2 的电源电压为 3.3 V,最大输出电流至少 500 mA。

建议在总电源入口处添加 ESD 保护器件和至少 10 μF 的大电容。

电源管理如 ESP32-S2 系列芯片技术规格书 > 图 ESP32-S2 电源管理 所示。

有关电源管脚的更多信息,请查看 ESP32-S2 系列芯片技术规格书 > 章节 电源。

数字电源

ESP32-S2 的管脚 27 VDD3P3_RTC_IO 和管脚 45 VDD3P3_CPU 为数字电源管脚,工作电压范围为 3.0 V ~ 3.6 V 和 2.8 V ~ 3.6 V。建议在电路中靠近数字电源管脚处添加 0.1 μF 电容。

管脚 VDD_SPI 可配置输出 1.8 V 或 3.3 V(默认)给外部电路使用。建议靠近该电源管脚处添加 0.1 μF 及 1 μF 去耦电容,请不要添加过大的电容。

当 VDD_SPI 处于 1.8 V 模式时,由 ESP32-S2 内部的 LDO 供电,能提供的典型电流值为 40 mA。

当 VDD_SPI 处于 3.3 V 模式时,由 VDD3P3_RTC 通过芯片内部的约 5 Ω 电阻后供电。因此 VDD_SPI 相对 VDD3P3_RTC 会有一定电压降。

注意

当使用 VDD_SPI 给封装内或封装外的 3.3 V flash/PSRAM 供电时,考虑到上文提到的电压降,为了满足 flash/PSRAM 的工作电压要求,请保证 VDD3P3_RTC 在 3.0 V 以上。

请注意 VDD3P3_RTC 不能单独供电工作,所有电源必须全部上电。

VDD_SPI 也可以连接到外部电源,由外部电源输入供电。

推荐使用 VDD_SPI 输出电源给封装外或封装内 flash/PSRAM 供电。

模拟电源

ESP32-S2 的 VDDA、VDD3P3 和 VDD3P3_RTC 管脚 为模拟电源管脚,工作电压范围为 2.8 V ~ 3.6 V。

对于 VDD3P3,当 ESP32-S2 工作在 TX 时,瞬间电流会加大,往往引起电源的轨道塌陷。所以在电路设计时建议在 VDD3P3 的电源走线上增加一个 10 μF 电容,该电容可与 0.1 μF 电容或其他电容搭配使用。

建议在总电源入口添加另一个 10 μF 电容。如果总电源入口靠近 VDD3P3,可以合并仅使用一个 10 μF 电容。

另外,在靠近 VDD3P3 处还需添加 LC 滤波电路,用于抑制高频谐波,同时请注意该电感的额定电流最好在 500 mA 及以上。

其余电容电路请参考 ESP32-S2 系列芯片参考设计原理图。

上电时序与复位

ESP32-S2 的 CHIP_PU 管脚为高电平时使能芯片,为低电平时复位芯片。

当 ESP32-S2 使用 3.3 V 系统电源供电时,电源轨需要一些时间才能稳定,之后才能拉高 CHIP_PU,激活芯片。因此,CHIP_PU 管脚上电要晚于系统电源 3.3 V 上电。

复位芯片时,复位电压 VIL_nRST 范围应为 (–0.3 ~ 0.25 × VDD) V。为防止外界干扰引起重启,CHIP_PU 管脚引线需尽量短一些。

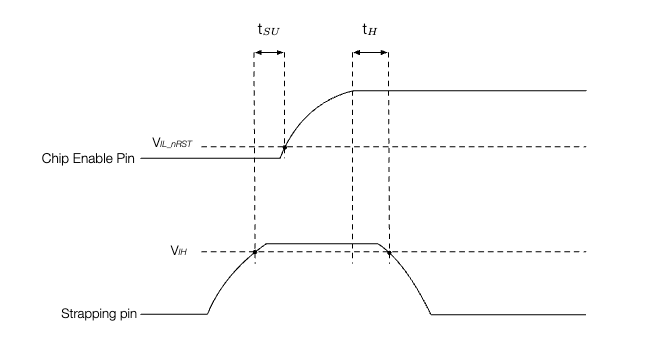

图 ESP32-S2 系列芯片上电和复位时序图 为 ESP32-S2 系列芯片的上电、复位时序图。

ESP32-S2 系列芯片上电和复位时序图

上电和复位时序参数说明见表 上电和复位时序参数说明。

参数 |

说明 |

最小值 (µs) |

|---|---|---|

tSTBL |

CHIP_PU 管脚上电晚于电源管脚上电的延时时间 |

50 |

tRST |

CHIP_PU 电平低于 VIL_nRST 从而复位芯片的时间 |

50 |

注意

CHIP_PU 管脚不可浮空。

为确保芯片上电和复位时序正常,一般采用的方式是在 CHIP_PU 管脚处增加 RC 延迟电路。RC 通常建议为 R = 10 kΩ,C = 1 μF,但具体数值仍需根据实际的电源特性配合芯片的上电、复位时序进行调整。

如果应用中存在以下场景:

电源缓慢上升或下降,例如电池充电;

需要频繁上下电的操作;

供电电源不稳定,例如光伏发电。

此时,仅仅通过 RC 电路不一定能满足时序要求,有概率会导致芯片无法进入正常的工作模式。此时,需要增加一些额外的电路设计,比如:

增加复位芯片或者看门狗芯片,通常阈值为 3.0 V 左右;

通过按键或主控实现复位等。

Flash 及 PSRAM

ESP32-S2 系列芯片需配合封装内或封装外 flash 一起使用,用于存储应用的固件和数据。封装内 PSRAM 和封装外 PSRAM 非必需。

封装外 Flash 及 PSRAM

为了减少软件适配的风险,推荐使用乐鑫官方适配过的 flash 和 PSRAM 型号,具体选型请咨询商务或者技术团队。如果使用 VDD_SPI 输出电压供电,设计时请注意需根据设置的 VDD_SPI 模式 (1.8 V/3.3 V) 选择合适的封装外 flash/PSRAM。另外,建议 SPI 通信线上预留 0 Ω 串联电阻,以便在需要时进行灵活调整,实现降低驱动电流、减小对射频的干扰、调节时序、提升抗干扰能力等功能。

目前,ESP32-S2-WROVER 模组默认采用 4 MB 的 SPI flash 及 2 MB 的 PSRAM。

图 ESP32-S2 Flash 及 SRAM 电路 为 ESP32-S2 系列芯片的 flash 及 SRAM 电路图。

ESP32-S2 Flash 及 SRAM 电路

时钟源

ESP32-S2 外部可以有两个时钟源:

外置主晶振时钟源(必选)

目前 ESP32-S2 系列芯片固件仅支持 40 MHz 晶振。

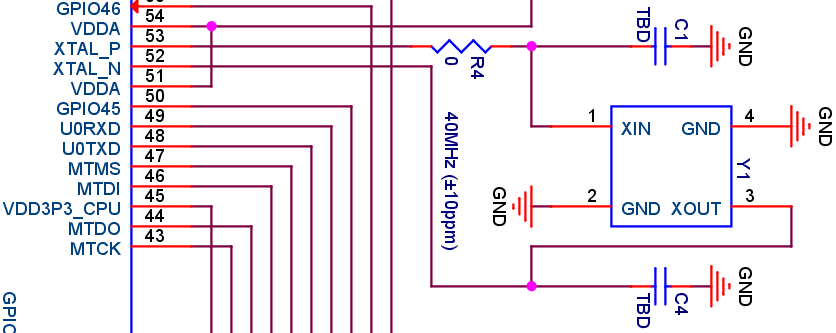

ESP32-S2 的无源晶振部分电路如图 ESP32-S2 系列芯片无源晶振电路图。注意,选用的无源晶振自身精度需在 ±10 ppm。

ESP32-S2 系列芯片无源晶振电路图

XTAL_P 时钟走线上请放置一个串联元器件,初始建议使用 24 nH 电感,用来减弱晶振高频谐波对射频性能的影响,最终值需要通过测试后确认。

外部匹配电容 C1 和 C4 的初始值可参考以下公式来决定:

其中 CL (负载电容)的值可查看所选择晶振的规格书,Cstray 的值为 PCB 的寄生电容。C1 和 C4 的最终值需要通过对系统测试后进行调节确定。调试方法如下:

通过 认证测试工具,选择 TX tone 模式。

使用综测仪或者频谱仪查看 2.4 GHz 信号,解调得到实际频偏。

通过调整外置负载电容,把频偏调整到 ±10 ppm(建议)以内。

当中心频率偏正时,说明等效负载电容偏小,需要增加外置负载电容。

当中心频率偏负时,说明等效负载电容偏大,需要减小外置负载电容。

通常两个外置负载电容相等,在特殊情况下,也可以有略微差异。

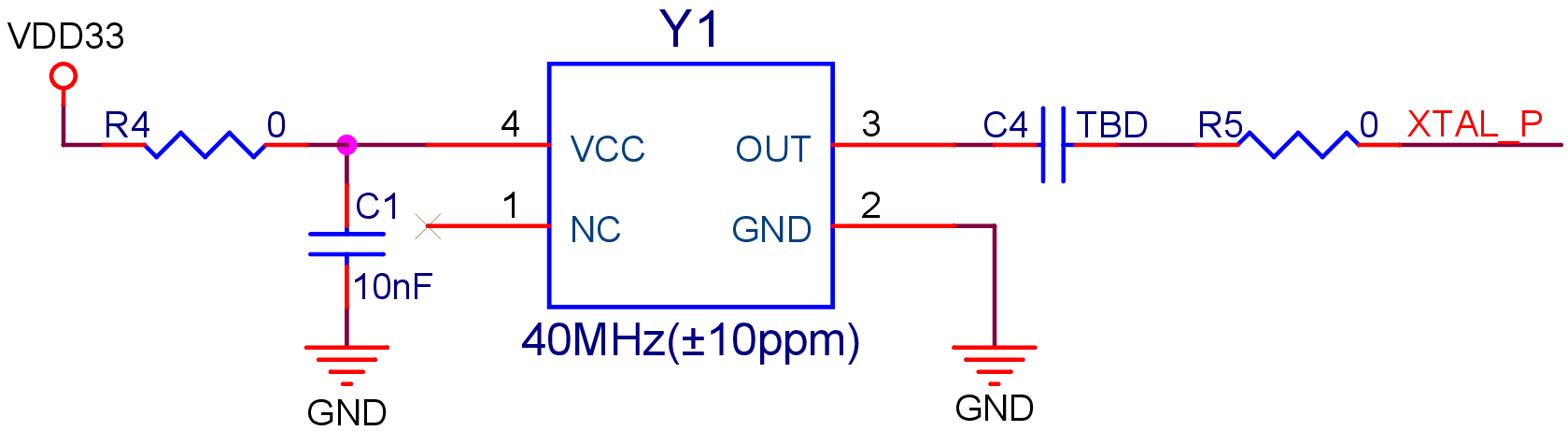

如需使用有源晶振,则将有源晶振的时钟输出通过一个隔直电容(50 pF 左右)连接至芯片端的 XTAL_P 端,XTAL_N 悬空即可。注意需要保证该有源晶振的输出时钟稳定且精度在 ±10 ppm 以内。另外,建议用户做好外接无源晶振的兼容设计,以防有源晶振电路出现问题时仍可以替换为无源晶振工作。ESP32-S2 的有源晶振部分电路如图 ESP32-S2 系列芯片有源晶振电路图。

ESP32-S2 系列芯片有源晶振电路图

备注

尽管 ESP32-S2 内部带有自校准功能,但是自身频偏过大(例如大于 ±10 ppm)、工作温度范围内稳定度不高等晶振本身的质量问题仍然会影响芯片的正常工作,导致射频指标性能下降。

建议晶振的幅值大于 500 mV。

如果出现功能性的 Wi-Fi 或蓝牙无法连接,排除软件原因后,可以采用上文中的方法,通过调节晶振的电容来保证频偏满足要求。

RTC 时钟源(可选)

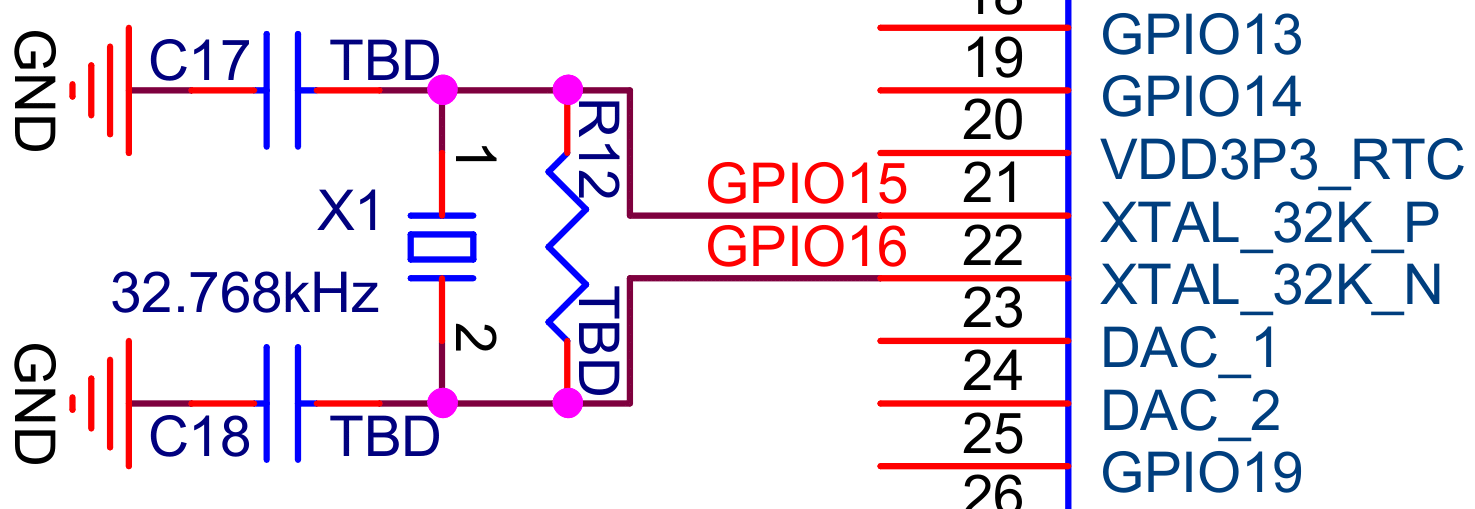

ESP32-S2 支持外置 32.768 kHz 的无源晶振作为 RTC 时钟。使用外部 RTC 时钟源是为了使时间更准确,从而降低平均功耗,但对于功能没有任何影响。

外置 32.768 kHz 无源晶振的电路如图 ESP32-S2 系列芯片外置 32.768 kHz 无源晶振电路图 所示。

ESP32-S2 系列芯片外置 32.768 kHz 无源晶振电路图

请注意 32.768 kHz 晶振选择要求:

等效内阻 (ESR) ≤ 70 kΩ。

两端负载电容值根据晶振的规格要求进行配置。

并联电阻 R 用于偏置晶振电路,电阻值要求 5 MΩ < R ≤ 10 MΩ。

该电阻一般无需上件。

如果不需要该 RTC 时钟源,则 32.768 kHz 晶振的管脚也可配置为通用 GPIO 口使用。

射频

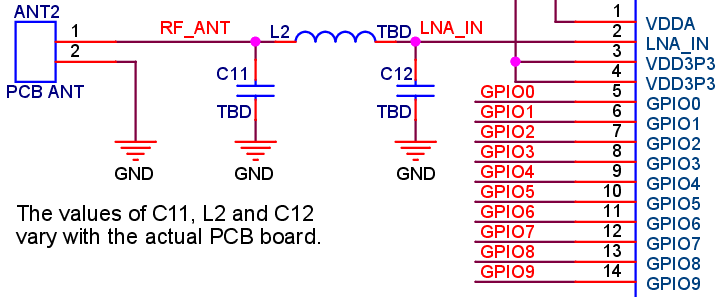

射频电路

ESP32-S2 系列芯片的射频电路主要由三部分组成:PCB 板射频走线、芯片匹配电路、天线及其匹配电路。各部分电路应满足以下设计规范:

PCB 板射频走线:需进行 50 Ω 阻抗控制。

芯片匹配电路:请尽量靠近芯片放置,优先采用 CLC 结构。

CLC 结构主要用于阻抗匹配及谐波抑制,空间允许的情况下可以再加一组 LC。

芯片匹配电路如图 ESP32-S2 系列芯片射频匹配电路图 所示。

天线及其匹配电路:为保证辐射性能,建议天线的输入阻抗为 50 Ω 左右。为保险起见,推荐在靠近天线位置增加一组 CLC 匹配电路,用于调节天线的输入阻抗。如果经过仿真可以确保天线阻抗点为 50 Ω 左右,并且空间较小,则可以不加天线端的匹配电路。

ESP32-S2 系列芯片射频匹配电路图

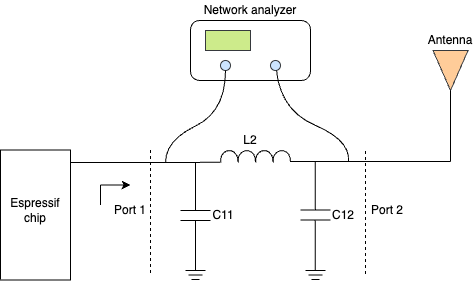

射频调试

射频匹配网络的参数值和 PCB 板有关,不要直接使用模组的匹配值,须按照下述射频调试进行确认。

图 ESP32-S2 射频调试示意图 展示了射频调试的大概过程。

ESP32-S2 射频调试示意图

将芯片匹配电路靠近芯片的端口定义为端口 1,将其靠近天线的端口定义为端口 2,则 S11 用来描述从端口 1 反射回来的信号功率与输入信号功率之比,如果匹配阻抗与芯片阻抗共轭,则传输性能最佳。S21 用来描述从端口 1 到端口 2 的信号功率传输损耗。如果 S11 接近芯片共轭阻抗点 35+j0,且 S21 在 4.8 GHz 和 7.2 GHz 频率下小于 -35 dB,则匹配电路可满足传输要求。

将芯片匹配电路的两端分别接到综测仪上,测试其信号反射参数 S11 及传输参数 S21。调试该匹配电路中元件的数值,直至 S11 和 S21 满足上述要求。如果芯片的 PCB 板严格设计遵循章节 PCB 版图布局 里的规范,用户可以参考表 匹配电路元器件推荐数值范围 来调试该匹配电路。

位号 |

推荐数值范围 |

物料编号 |

|---|---|---|

C11 |

1.2 ~ 1.8 pF |

GRM0335C1H1RXBA01D |

L2 |

2.4 ~ 3.0 nH |

LQP03TN2NXB02D |

C12 |

1.8 ~ 1.2 pF |

GRM0335C1H1RXBA01D |

射频匹配器件请采用 0201 物料,芯片端匹配电路的第一个电容需要添加枝节。

备注

如果不需要射频功能,建议不要在固件中初始化射频堆栈。此时,射频管脚可以悬空。如果启用射频功能,请确保已连接天线,否则可能导致系统不稳定或射频电路损坏。

UART

UART0 通常作为下载和 log 打印的串口。关于如何使用 UART0 进行下载,请参考章节 下载指导。U0TXD 线上建议串联 499 Ω 电阻用于抑制谐波。

推荐使用其他 UART 作为通信的串口,同样在 TX 线上建议预留串联电阻用于抑制谐波。

GPIO18 作为 U1RXD,在芯片上电时是不确定状态,可能会影响芯片正常进入下载启动模式,需要在外部增加一个上拉电阻来解决。

请注意使用 AT 固件时,固件里配置了 UART 的 GPIO,可以参考 硬件连接,建议使用默认配置。

SPI

在使用 SPI 功能时,为了提高 EMC 性能,请在 SPI_CLK 线上添加串联电阻(或磁珠)以及对地电容。如果空间允许,建议在其他 SPI 线上也添加串联电阻和对地电容。另外,请确保 RC/LC 器件靠近芯片或模组的管脚放置。

Strapping 管脚

芯片每次上电或复位时,都需要一些初始配置参数,如加载芯片的启动模式等。这些参数通过 strapping 管脚控制。复位放开后,strapping 管脚和普通 IO 管脚功能相同。

GPIO0、GPIO45 和 GPIO46 为 strapping 管脚。

所有的 strapping 管脚信息,可参考 ESP32-S2 系列芯片技术规格书 > 章节 启动配置项。

下面主要介绍和启动模式有关的 strapping 管脚信息。

芯片复位释放后,GPIO0 和 GPIO46 共同决定启动模式,详见表 芯片启动模式控制。

启动模式 |

GPIO0 |

GPIO46 |

|---|---|---|

默认配置 |

1(上拉) |

0(下拉) |

SPI Boot |

1 |

任意值 |

Download Boot |

0 |

0 |

无效组合 1 |

0 |

1 |

- 1

该组合会触发意外行为,应当避免。

Strapping 管脚的时序参数包括 建立时间 和 保持时间。更多信息,详见图 Strapping 管脚的时序参数图 和表 Strapping 管脚的时序参数说明。

参数 |

说明 |

最小值 (ms) |

|---|---|---|

tSU |

建立时间,即拉高 CHIP_PU 激活芯片前,电源轨达到稳定所需的时间 |

0 |

tH |

保持时间,即 CHIP_PU 已拉高、strapping 管脚变为普通 IO 管脚开始工作前,可读取 strapping 管脚值的时间 |

3 |

注意

建议在 GPIO0 管脚处预留上拉电阻。

不要在 GPIO0 管脚处添加较大的电容,可能会导致进入下载模式。

GPIO

ESP32-S2 系列芯片通过 IO MUX 表格或者 GPIO 交换矩阵来配置 GPIO。IO MUX 是默认的外设管脚配置(详见 ESP32-S2 系列芯片技术规格书 > 附录 ESP32-S2 管脚总览),GPIO 交换矩阵用于将可以配置的外设信号传输至 GPIO 管脚。更多关于 IO MUX 和 GPIO 交换矩阵的信息,请参考 ESP32-S2 技术参考手册 > 章节 IO MUX 和 GPIO 交换矩阵。

部分外设的 GPIO 管脚是固定的,部分是可以任意配置的,具体信息请参考 ESP32-S2 系列芯片技术规格书 > 章节 外设。

使用 GPIO 时,请注意:

Strapping 管脚的上电状态。

请注意 GPIO 复位后的默认配置,详见下表。建议对处于高阻态的管脚配置上拉或下拉,或在软件初始化时开启管脚自带的上下拉,以避免不必要的耗电。

避免使用 flash/PSRAM 占用的管脚。

GPIO33 ~ GPIO37 属于同一电源域,即 VDD3P3_CPU,也可由软件配置为 VDD_SPI。

管脚序号 |

管脚名称 |

管脚类型 |

电源域 |

复位时 |

复位后 |

数字功能 0 |

RTC |

模拟 |

|---|---|---|---|---|---|---|---|---|

1 |

VDDA |

电源 |

||||||

2 |

LNA_IN |

电源 |

||||||

3 |

VDD3P3 |

电源 |

||||||

4 |

VDD3P3 |

电源 |

||||||

5 |

GPIO0 |

IO |

VDD3P3_RTC_IO |

IE, WPU |

IE, WPU |

IO MUX |

RTC |

|

6 |

GPIO1 |

IO |

VDD3P3_RTC_IO |

IE |

IE |

IO MUX |

RTC |

模拟 |

7 |

GPIO2 |

IO |

VDD3P3_RTC_IO |

IE |

IE |

IO MUX |

RTC |

模拟 |

8 |

GPIO3 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

9 |

GPIO4 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

10 |

GPIO5 |

IO |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

11 |

GPIO6 |

IO |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

12 |

GPIO7 |

IO |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

13 |

GPIO8 |

IO |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

14 |

GPIO9 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

15 |

GPIO10 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

16 |

GPIO11 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

17 |

GPIO12 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

18 |

GPIO13 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

19 |

GPIO14 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

20 |

VDD3P3_RTC |

电源 |

||||||

21 |

XTAL_32K_P |

模拟 |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

22 |

XTAL_32K_N |

模拟 |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

23 |

DAC_1 |

IO |

VDD3P3_RTC_IO |

IE |

IO MUX |

RTC |

模拟 |

|

24 |

DAC_2 |

IO |

VDD3P3_RTC_IO |

IE, WPU |

IO MUX |

RTC |

模拟 |

|

25 |

GPIO19 |

IO |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

26 |

GPIO20 |

IO |

VDD3P3_RTC_IO |

IO MUX |

RTC |

模拟 |

||

27 |

VDD3P3_RTC_IO |

电源 |

||||||

28 |

GPIO21 |

IO |

VDD3P3_RTC_IO |

IO MUX |

RTC |

|||

29 |

SPICS1 |

IO |

VDD_SPI |

IE, WPU |

IE, WPU |

IO MUX |

||

30 |

VDD_SPI |

电源 |

||||||

31 |

SPIHD |

IO |

VDD_SPI |

IE, WPU |

IE, WPU |

IO MUX |

||

32 |

SPIWP |

IO |

VDD_SPI |

IE, WPU |

IE, WPU |

IO MUX |

||

33 |

SPICS0 |

IO |

VDD_SPI |

IE, WPU |

IE, WPU |

IO MUX |

||

34 |

SPICLK |

IO |

VDD_SPI |

IE, WPU |

IE, WPU |

IO MUX |

||

35 |

SPIQ |

IO |

VDD_SPI |

IE, WPU |

IE, WPU |

IO MUX |

||

36 |

SPID |

IO |

VDD_SPI |

IE, WPU |

IE, WPU |

IO MUX |

||

37 |

GPIO33 |

IO |

VDD_SPI / VDD3P3_CPU |

IE |

IO MUX |

|||

38 |

GPIO34 |

IO |

VDD_SPI / VDD3P3_CPU |

IE |

IO MUX |

|||

39 |

GPIO35 |

IO |

VDD_SPI / VDD3P3_CPU |

IE |

IO MUX |

|||

40 |

GPIO36 |

IO |

VDD_SPI / VDD3P3_CPU |

IE |

IO MUX |

|||

41 |

GPIO37 |

IO |

VDD_SPI / VDD3P3_CPU |

IE |

IO MUX |

|||

42 |

GPIO38 |

IO |

VDD3P3_CPU |

IE |

IO MUX |

|||

43 |

MTCK |

IO |

VDD3P3_CPU |

IE |

IO MUX |

|||

44 |

MTDO |

IO |

VDD3P3_CPU |

IE |

IO MUX |

|||

45 |

VDD3P3_CPU |

电源 |

||||||

46 |

MTDI |

IO |

VDD3P3_CPU |

IE |

IO MUX |

|||

47 |

MTMS |

IO |

VDD3P3_CPU |

IE |

IO MUX |

|||

48 |

U0TXD |

IO |

VDD3P3_CPU |

IE, WPU |

IE, WPU |

IO MUX |

||

49 |

U0RXD |

IO |

VDD3P3_CPU |

IE, WPU |

IE, WPU |

IO MUX |

||

50 |

GPIO45 |

IO |

VDD3P3_CPU |

IE, WPD |

IE, WPD |

IO MUX |

||

51 |

VDDA |

电源 |

||||||

52 |

XTAL_N |

IO |

||||||

53 |

XTAL_P |

IO |

||||||

54 |

VDDA |

电源 |

||||||

55 |

GPIO46 |

IO |

VDD3P3_CPU |

IE, WPD |

IE, WPD |

IO MUX |

||

56 |

CHIP_PU |

模拟 |

||||||

57 |

GND |

电源 |

ADC

使用 ADC 功能时,请靠近管脚添加 0.1 μF 的对地滤波电容,精度会更准确一些。

USB

ESP32-S2 系列芯片带有一个集成了收发器的全速 USB On-The-Go (OTG) 外设,符合 USB 1.1 规范。

GPIO19 和 GPIO20 可以分别作为 USB 的 D- 和 D+,线上建议预留串联电阻(初始值可为 22/33 Ω)和对地电容(初始可不上件),并注意靠近芯片端放置。

请注意 USB_D+ 管脚上电时会输出高低电平信号,其中高电平的状态比较强,需要较强的下拉才可以拉低。因此,如果需要一个稳定的初始状态,建议添加外部上拉来提供稳定的高电平初始值。

ESP32-S2 系列芯片也支持将 GND、RXD、TXD 接出外接 USB 转 UART 进行下载和 log 打印,下载指导请参考章节 下载指导。

触摸传感器

ESP32-S2 提供了多达 14 个电容式传感 GPIO,能够探测由手指或其他物品直接接触或接近而产生的电容差异。这种设计具有低噪声和高灵敏度的特点,可以用于支持使用相对较小的触摸板。设计中也可以使用触摸板阵列以探测更大区域或更多点。

ESP32-S2 的触摸传感器同时还支持防水和数字滤波等功能来进一步提高传感器的性能。

注意

ESP32-S2 触摸传感器目前尚无法通过射频抗扰度测试系统 (CS) 认证,应用场景有所限制。

触摸传感器功能对应的 GPIO 管脚如下表所示。

GPIO 管脚 |

触摸传感器功能 |

|---|---|

GPIO1 |

TOUCH1 |

GPIO2 |

TOUCH2 |

GPIO3 |

TOUCH3 |

GPIO4 |

TOUCH4 |

GPIO5 |

TOUCH5 |

GPIO6 |

TOUCH6 |

GPIO7 |

TOUCH7 |

GPIO8 |

TOUCH8 |

GPIO9 |

TOUCH9 |

GPIO10 |

TOUCH10 |

GPIO11 |

TOUCH11 |

GPIO12 |

TOUCH12 |

GPIO13 |

TOUCH13 |

GPIO14 |

TOUCH14 |

注意只有 GPIO14 (TOUCH14) 可以驱动屏蔽电极。

使用 TOUCH 功能时,建议靠近芯片侧预留串联电阻,用于减小线上的耦合噪声和干扰,也可加强 ESD 保护。该阻值建议 470 Ω 到 2 kΩ,推荐 510 Ω。具体值还需根据产品实际测试效果而定。