Chip Revision Identification

Espressif is introducing a new vM.X numbering scheme to indicate chip revisions. This guide outlines the structure of this scheme and provides information on chip errata and additional identification methods.

Chip Revision Numbering Scheme

The new numbering scheme vM.X consists of the major and minor numbers described below.

M – Major number, indicating the major revision of the chip product. If this number changes, it means the software used for the previous version of the product is incompatible with the new product, and the software version shall be upgraded for the use of the new product.

X – Minor number, indicating the minor revision of the chip product. If this number changes, it means the software used for the previous version of the product is compatible with the new product, and there is no need to upgrade the software.

The vM.X scheme replaces previously used chip revision schemes, including ECOx numbers, Vxxx, and other formats if any.

Primary Identification Methods

eFuse Bits

The chip revision is encoded using four eFuse fields:

EFUSE_BLK0_RDATA5[25:24]

EFUSE_BLK0_RDATA5[20]

EFUSE_BLK0_RDATA3[15]

APB_CTRL_DATE[31]

eFuse Bit |

Chip Revision |

|||||

|---|---|---|---|---|---|---|

v0.0 |

v1.0 |

v1.1 |

v3.0 |

v3.1 |

||

Major Number |

APB_CTRL_DATE[31] |

0 |

0 |

0 |

1 |

1 |

EFUSE_BLK0_RDATA5[20] |

0 |

0 |

0 |

1 |

1 |

|

EFUSE_BLK0_RDATA3[15] |

0 |

1 |

1 |

1 |

1 |

|

Minor Number |

EFUSE_BLK0_RDATA5[25] |

0 |

0 |

0 |

0 |

0 |

EFUSE_BLK0_RDATA5[24] |

0 |

0 |

1 |

0 |

1 |

|

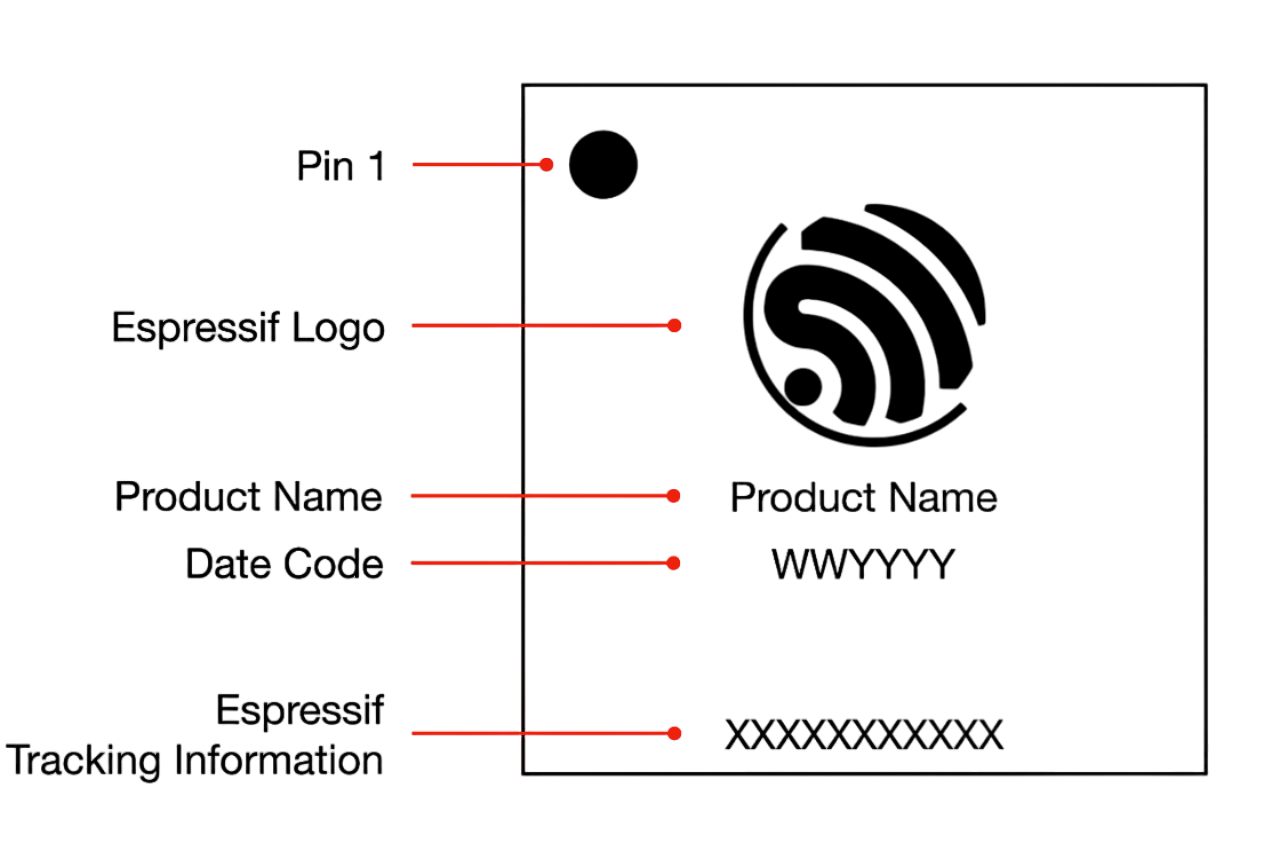

Chip Marking

Espressif Tracking Information line in chip marking

Figure 1 Chip Marking Diagram

Chip Revision |

Espressif Tracking Information |

|---|---|

v0.0 |

XXXXXXXX |

v1.0 |

X |

v1.1 |

X |

v3.0 |

X |

v3.1 |

X |

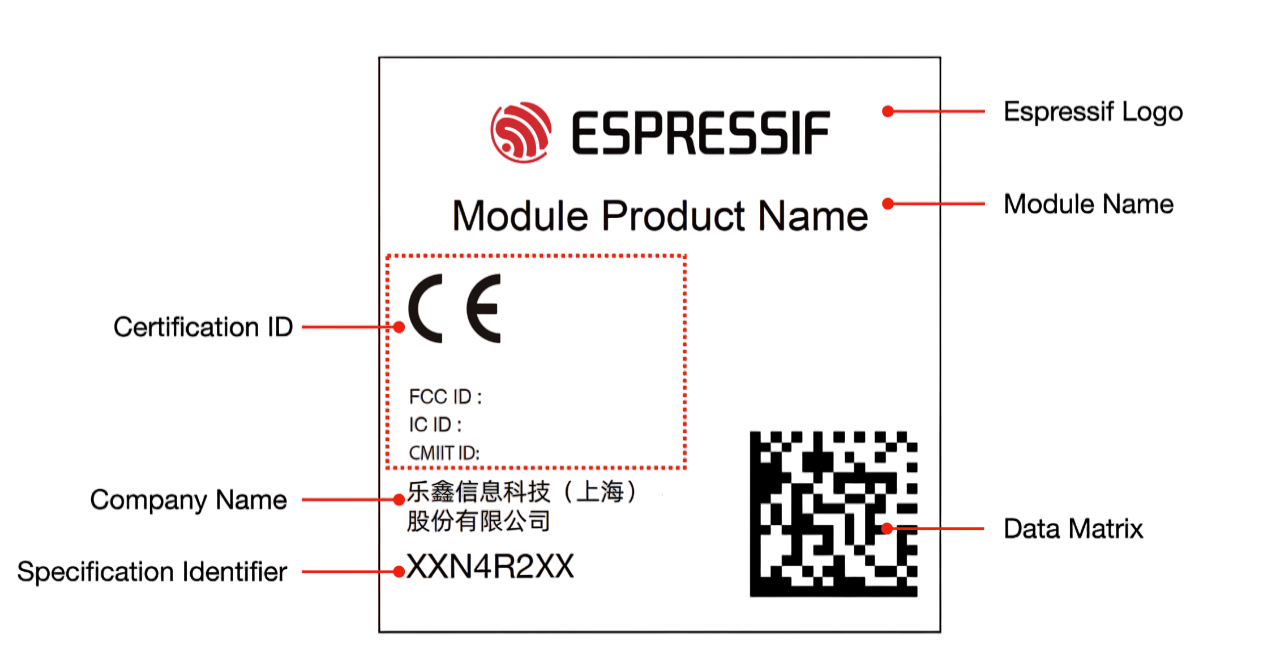

Module Marking

Specification Identifier line in module marking

Figure 2 Module Marking Diagram

Table 3 Chip Revision Identification by Module Marking Chip Revision

Specification Identifier

v0.0

XXXXXX 1

v1.0

XXXXXX

v1.1

MFXXXXv3.0

MEXXXXv3.1

MGXXXX1 To distinguish between v0.0 and v0.1, please check the eFuse bits.

Additional Identification Methods

Date Code

Some errors in the chip product don’t need to be fixed at the silicon level, or in other words in a new chip revision.

In this case, the chip may be identified by Date Code in chip marking (see Chip Marking). For more information, please refer to ESP32 Chip Packaging Information > Chip Silk Marking.

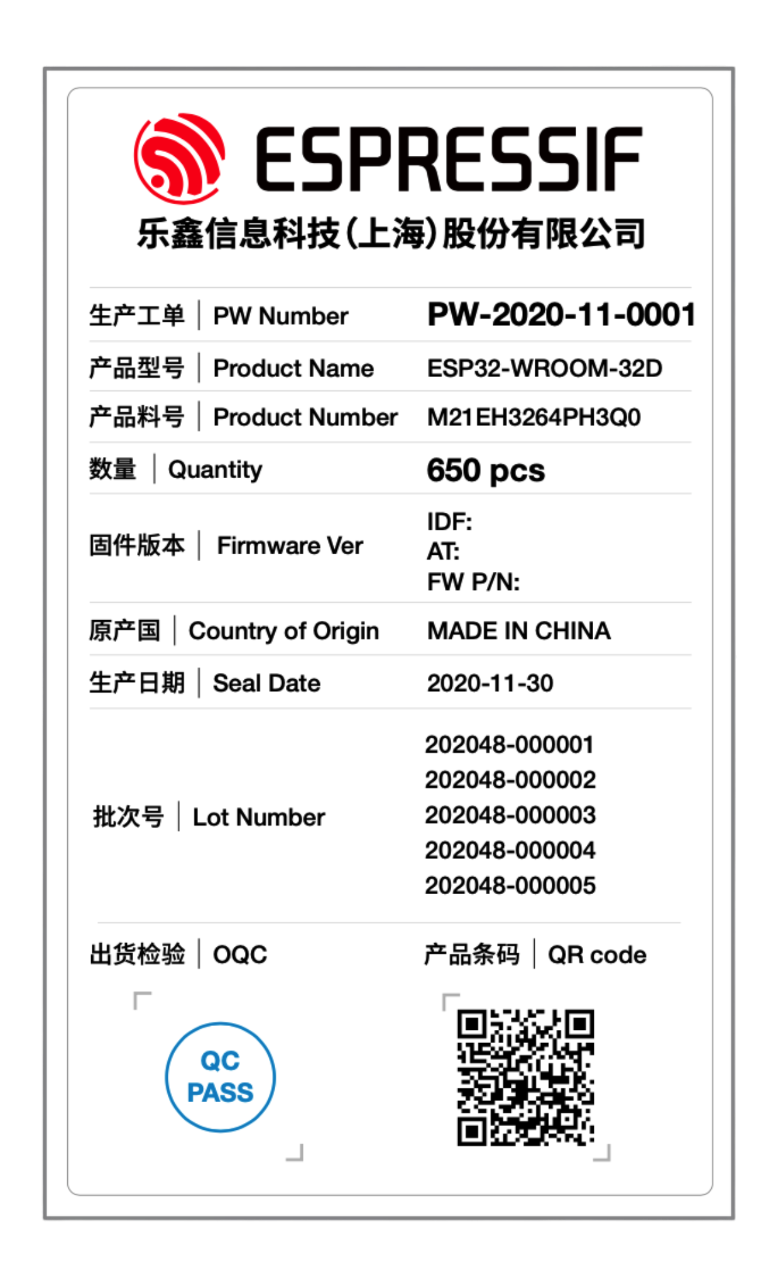

PW Number

Modules built around the chip may be identified by PW Number in product label (see Module Product Label). For more information, please refer to ESP32 Module Packaging Information > Pizza Box.

Figure 3 Module Product Label

Note

Please note that PW Number is only provided for reels packaged in aluminum moisture barrier bags (MBB).

ESP-IDF Release Compatibility

Information about ESP-IDF release that supports a specific chip revision is provided in Compatibility Between ESP-IDF Releases and Revisions of Espressif SoCs.