硬件设计

ESP32 中 I2S 信号管脚过于分散,是否可以配置集中⼀些,例如配置到 GPIO5、GPIO18、GPIO23、GPIO19、GPIO22 或者 GPIO25、GPIO26、GPIO32、GPIO33 管脚上?

所有 I2S 的 I/O 均可任意分配。需要注意的是,有的 I/O 只能作为输⼊,请参考 《ESP32 技术规格书》 的外设管脚分配章节和附录中的 IO_MUX 管脚清单。

ESP32 在 Light-sleep 模式下如何避免 VDD3P3_RTC 管脚的电压掉电?

ESP32 进⼊ Light-sleep 模式后,RTC 掉电会使 VDD3P3_RTC 管脚对应的 GPIO 的电平被拉低,从而导致外部 RTC 或者其他外设无法正常工作。可以采取以下两种方式解决该问题:

设置 RTC 硬件电压控制寄存器 RTC_CNTL_REG 来控制电压。具体来说,需要将 RTC_CNTL_REG 寄存器中的 FORCE_PU 和 FORCE_PD 位设置为 1,即

RTC_CNTL_REG |= RTC_CNTL_FORCE_PU_M | RTC_CNTL_FORCE_PD_M;。使用 GPIO 保持管脚。ESP32 的 Light-sleep 模式支持 GPIO 保持功能,可以将某些 GPIO 管脚设置为保持管脚,保持在系统进入低功耗模式时的电平状态。具体来说,可以将 VDD3P3_RTC 管脚设置为保持管脚,以保持其电压。相关代码片段如下:

esp_sleep_pd_config(ESP_PD_DOMAIN_RTC_PERIPH, ESP_PD_OPTION_ON); esp_sleep_enable_gpio_wakeup(); gpio_hold_en(GPIO_NUM_X);其中,ESP_PD_DOMAIN_RTC_PERIPH 表示 RTC 子系统的电源域,ESP_PD_OPTION_ON 表示使能电源域,gpio_hold_en() 函数可以将指定的 GPIO 管脚设置为保持管脚。将 VDD3P3_RTC 管脚设置为保持管脚之后,即使系统进入 Light-sleep 模式,该管脚的电压也会保持。

需要注意的是,使用 GPIO 保持功能会增加系统的功耗,因此需要根据具体的应用场景来选择合适的方案。如果只需要保持 RTC 硬件的电源供应,可以使用第一种方法;如果需要保持其他外设的电源供应,可以使用第二种方法。

配置 ESP32 管脚有什么注意事项?

大部分数字外设可以通过 GPIO 交换矩阵配置到任意管脚。SDIO、SPI 高速以及模拟类相关功能只能通过 IO MUX 切换使用。

管脚使用注意事项可参考 GPIO & RTC GPIO 说明。

备注

Strapping 管脚的默认电平,详情参考 《ESP32 技术规格书》。

GPIO34 ~ GPIO39(⽤作输⼊ IO,并且无上下拉功能)。

GPIO6 ~ GPIO11 由 flash 管脚占⽤。

GPIO1 和 GPIO3 是 UART0 的 TX 和 RX 管脚,⽆法进行配置。

对于带有 PSRAM 的模组,GPIO16 和 GPIO17 由 PSRAM 占⽤。

乐鑫芯片 GPIO 最大承载电压是多少?

GPIO 最大耐压设计为 3.6 V。超出部分建议从硬件设计上补充分压电路,否则会造成 GPIO 损坏。

ESP8266 电压电流需求?

ESP8266 的数字部分的电压范围是 1.8 V ~ 3.3 V。

模拟部分的⼯作电压是 3.0 V ~ 3.6 V,最低 2.7 V。

模拟电源峰值 350 mA。

数字电源峰值 200 mA。

备注

选择的 SPI flash ⼯作电压也需要与 GPIO 的电压匹配。CHIP_EN ⼯作在 3.0 V ~ 3.6 V,使⽤ 1.8 V GPIO 控制时需要注意电平转换。

乐鑫 Wi-Fi 模组是否有单面板 PCB 的方案?

ESP32 属于无线模块,射频性能对于 PCB 材质有较高的要求。我们测试过 4 层与 2 层的方案,但未测试过单层的设计。

在此不建议使用单层板子的方案,建议产品 PCB 可以使用单层板,贴装我们的模组。单层板子的模组,射频性能无法预估。

为保证良好的 RF 性能,我们建议使用 4 层板设计。

使用电池为 ESP8266 供电有哪些注意事项?

ESP8266 电压范围为 3.0 V ~ 3.6 V,两节 AA 电池可以给 ESP8266 供电。需要注意电池压降是否满足芯片电压范围。

锂电池电压范围超过模组要求,并且放电时压降较⼤,不适合直接给 ESP8266 供电。

推荐电池使⽤ DC/DC 或 LDO 升降压后给 ESP8266 供电,并且注意电源芯片压差要求。

如何获取 ESP32 系列芯片 footprint?

可以在 模组设计 中下载芯片对应的模组参考设计,里面有管脚封装设计。

使用 ESP32-S2 芯片,用了 DVP camera 接口后还能接入语音吗?

ESP32-S2 的 LCD 接口、DVP camera 接口和 I2S 接口共用一套硬件资源,只能同时支持其中一个。

使用 ESP32 模块,使用 GPIO0 和 GPIO4 作为 I2C 信号接口,需要注意什么?

作为 I2C 信号接口时,GPIO0 需要上拉。烧写时,只要保证上电时 GPIO0 能拉低,然后便可释放。GPIO0 无需一直拉低,只有下载的时候需要拉低。

ESP32 的外接 flash 占用了 GPIO6 ~ GPIO11,这 6 个 GPIO 是否还能作为 SPI 来使用?

ESP32 的外接 flash 占用了 GPIO6 ~ GPIO11,这 6 个 GPIO 就不能再作为 SPI 来使用了。

使用 ESP8285 芯片时,是否需要连接外部晶振?

ESP8285 芯片内部无晶振,需要连接外部晶振。

ESP32-D2WD 外接 PSRAM 的参考设计?

建议参考 《ESP32-PICO-D4 技术规格书》 的外围设计原理图章节。

备注

ESP32-D2WD 是 1.8 V flash,所以 VDD_SDIO 需要加电阻和电容,并且连接 1.8 V PSRAM。

ESP32 是否可以用 PWM 或 DAC 来播放音乐?

ESP32 可以用 PWM 或 DAC 来播放音乐,推荐用于提示音播放,可基于 esp-adf/examples/player/pipeline_play_mp3_with_dac_or_pwm 例程进行测试。

为什么 ESP32 模组和 ESP32 芯片的建议工作电压范围不一样?

因为它们的工作环境和使用方式不同。

ESP32 芯片是一颗裸片,需要在电路板上加上外围电路才能正常工作。ESP32 芯片的建议工作电压范围为 2.3 V 至 3.6 V,是根据 ESP32 芯片本身的电气参数来决定的。在这个电压范围内,ESP32 芯片能够正常工作,并且可以提供最佳的性能和功耗表现。

ESP32 模组则是已经封装好的整个电路模块,通常会加上稳压电路、外部晶振、外部天线等外围电路,以及其他外设芯片(如 flash、RAM)等,可以直接使用。由于模组上的电路已经经过优化和调试,因此建议工作电压范围会更窄一些。例如,ESP32-WROOM-32 模组的建议工作电压范围就为 3.0 V 至 3.6 V。此外,由于模组要考虑 flash 的电压,所以 ESP32 模组的建议工作电压会更高一些。

在使用这些芯片和模组时,需要根据具体情况选择合适的电源和外围电路,以确保它们能够正常工作。

更多信息,请对比模组和芯片的 技术规格书。

自主设计模组 flash 擦除速度相比乐鑫模组较慢有哪些原因?

由于不同厂家 flash 器件存在差异,擦除扇区部分所需时间也各不相同,该时间差异属于正常现象。

如果希望擦除速度较快,可以测试不同厂家 flash 的擦除速度进行综合评估。

ESP8266 为何上电瞬间会电流较大?

ESP8266 的 RF 和数字电路具有极⾼的集成度,上电后 RF ⾃校准,在校准时会需要⼤电流。

模拟部分电路最⼤的极限电流可能达到 500 mA,数字电路部分最⼤电流达到 200 mA。

常规应用时,平均电流约 100 mA。

综上,ESP8266 电源设计需要满足 500 mA 电流。

ESP32 以太网 RMII 时钟选择有哪些?

硬件设计上建议使用 GPIO0 作为 RMII 时钟输入的管脚,请注意 GPIO0 在芯片上电时不可为低电平。

详细说明请阅读 配置 MAC 与 PHY 指南。

ESP32-LyraT 开发板扬声器接口规格?

接口使用 PH-2A 规格连接器。

基于 ESP32 设计的模组,哪些管脚无法被用户使用?

ESP32-WROOM 系列模组,GPIO6 ~ GPIO11 为 flash 管脚,作为 flash 通信使⽤,不可被用户使用。

ESP32-WROVER 系列模组,GPIO16 和 GPIO17 被模组 PSRAM 占⽤,不可被用户使用。

此外,ESP32 有 5 个 Strapping 管脚,在使⽤时需要额外注意,具体细节请参考 《ESP32 技术规格书》。

ESP32 如何使用管脚复位芯片?

ESP32 的复位可使用 CHIP_PU 管脚。当 CHIP_PU 为低电平时,复位电平 (VIL_nRST) 要求足够低,并且持续一段时间。注意:该管脚不可浮空。可参见 《ESP32 硬件设计指南》 中的 复位 章节。

ESP8266 供电设计需要注意哪些问题?

如果是使⽤ LDO 变压,请确保输⼊电压在 (2.7 V ~ 3.6 V) 和输出电流(大于 500 mA)要⾜够⼤。

电源轨去耦电容器必须接近 ESP8266 摆放,等效电阻要⾜够低。

ESP8266 不能直连 5 V,仅支持 3.3 V,电压范围 2.7 V ~ 3.6 V。

如果是通过 DC-DC 给 ESP8266 供电,必要时要加上 LC 滤波电路。

可参考 《ESP8266 硬件设计指南》 中的 电源 章节。

ESP8266 使用 TOUT 管脚做 ADC 采样时,超过 0 V ~ 1.0 V 是否会损坏管脚?

输入电压在芯片管脚电压范围内均不会损坏管脚(默认为 0 V ~ 3.6 V)。

超过采样阈值将会影响采集的数据结果,导致数据结果异常。

使用板载天线的模组,对 PCB 和外壳设计有哪些要求?

如产品采⽤模组进⾏ on-board 设计,则需注意考虑模组在底板的布局,应尽可能地减⼩底板对模组 PCB 天线性能的影响。

条件允许的情况下,建议将模组 PCB 天线区域延伸出底板板框外,并将模组尽可能地靠近底板板边放置,使天线的馈点距离板边最近。

请确保模块不被任何⾦属的外壳包裹,模块 PCB 天线区域及外扩 15 mm 区域需净空(严禁铺铜、⾛线、摆放元件)。

具体说明请阅读对应模组的 硬件设计指南。

使用 ESP32 GPIO34 ~ GPIO39 是否可作为 UART 的 RX ?

GPIO34 ~ GPIO39 作为接收使用,可应用 UART 的 RX。

ESP32 模组外接 32 kHz 晶振参考设计?

请参考文档 RTC 时钟源(可选)(ESP32) 中的硬件设计说明。

ESP32 模组 flash 是否支持 80 MHz 的 QIO 模式?

ESP32 模组可以同时支持 flash 模式,QIO 和 flash 速度为 80 MHz。

使用 QIO 模式建议使用在二级 Bootloader 中开启,因为部分 flash 状态寄存器默认 QE 未置 1。

如何配置 ESP32 以太网的 RMII 同步时钟?

请下载 esp-idf/examples/ethernet/basic 例程进行测试。

IP101 PHY 芯片在 GPIO0 输出 CLK 时会出现网络不稳定的现象,所以推荐 PHY 外接 50 MHz 晶振,GPIO0 作为输入。

由于 GPIO0 的特殊性,所以需要配置 IO 控制 PHY 的使能管脚。

请阅读 以太网文档。

使用 ESP8266 芯片如何进行硬件复位?硬件复位信号是低电平有效还是高电平有效?复位的条件是什么?

ESP8266 的 Pin32 EXT_RSTB 为复位管脚。此管脚内部有上拉电阻,低电平有效。为防⽌外界⼲扰引起的重启,建议 EXT_RSTB 的⾛线尽量短,并在 EXT_RSTB 管脚处增加⼀个 RC 电路。

ESP8266 的 CHIP_EN 管脚也可作为硬件复位管脚,当使用 CHIP_EN 管脚作为复位管脚时,复位信号是低电平有效。复位条件为当输入电平低于 0.6 V 并持续 200 μs 以上时,ESP8266 会复位重启。我们推荐使用 CHIP_EN 管脚进行芯片复位。可参考 《ESP8266 硬件设计指南》 中的 复位 章节。

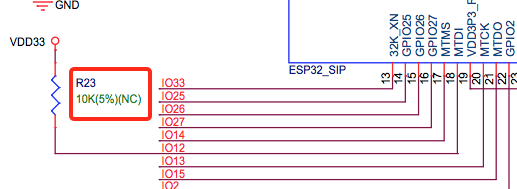

乐鑫原理图中的 NC 缩写是什么意思?

如何在 ESP32-S2 中使用多天线?

ESP32-S2 的多天线使用和 ESP32 类似,可以参考 《ESP32-WROOM-DA 技术规格书》 中的多天线使用。

《ESP-IDF 编程指南》 中提供了详细的操作说明。

使用时添加一个 RF 开关,通过开关选择具体工作的天线。

ESP32-C3F SPI CS0 是否需要外接 10 kΩ 上拉电阻?

ESP32-C3F 的 SPI 控制器支持软件可编程的 CS (Chip Select) 管脚,不需要外接 10 kΩ 上拉电阻。

在 ESP32-C3F 中,可以通过在 SPI 控制器配置中设置 CS 管脚为任意 GPIO 引脚,并在代码中通过设置 GPIO 状态来控制 CS 管脚的电平。当 SPI 总线空闲时,CS 管脚会自动被拉高至 GPIO 引脚的默认状态,不需要外接上拉电阻。

需要注意的是,在使用软件可编程的 CS 管脚时,需要在 SPI 总线传输前手动将 CS 管脚拉低,以选择目标设备,并在传输完成后将 CS 管脚拉高,以释放设备。同时,还需要根据实际情况调整 CS 管脚的电平和状态,以确保 SPI 总线的稳定性和可靠性。

ESP-Skainet 有语音识别硬件设计参考吗?

ESP32 芯片硬件设计是否有必要接 32 kHz 的 RTC 晶振?

外接 32 kHz 的 RTC 晶振是可选的,并非必选。其主要目的是提供更高的时间精度和降低功耗,核心应用场景包括:

低功耗蓝牙 (BLE) 设计:外接 32 kHz 晶振主要用于低功耗蓝牙的 Light-sleep 计时。如果硬件上不加 32 kHz 外部晶振,Light-sleep 模式在某些 BLE 应用中可能无法生效。

提高时间精度:与内部 RC 振荡器相比,外部晶振受环境影响更小,精度更高。这对于需要定时唤醒接收 Beacon(如 Wi-Fi/蓝牙保活)的应用至关重要,能有效防止因时钟漂移导致 RF 等待窗口期变长,从而显著降低平均功耗。

如果应用场景中不涉及低功耗模式或不需要在睡眠期间保持高精度计时,则完全可以不接。

ESP32 内部集成有 150 kHz RC 振荡器和 8.5 MHz 振荡器分频产生的时钟,可以作为 RTC 时钟源。虽然它们的频率稳定性受温度影响较大,但在非高精度要求的应用中可以替代外部 32 kHz 晶振。

使用 ESP32-MINI-1 模组,是否可提供 Altium Designer 的元件库?

我们的硬件原理图是在 PADS 中开发设计的,在 《ESP32-MINI-1 参考设计》 中有一个 ASC 的文件,可在 Altium Designer 里转换打开。

更多型号的模组的硬件设计资料可在 技术文档 中获取。

ESP8266 的 UART0 的输入电压能由 3.3 V 改为 1.8 V 吗?

UART0 的电源域是 VDDPST,VDDPST 理论上可以到 1.8 V,所以 UART0 理论上可以改成 1.8 V。

ESP8266 UART0 的电平是由 VDD 决定的,还是由 VDDPST 决定的?

ESP8266 UART0 的电平是由 VDDPST(硬件电源域)决定的,数字电源电压都是由 VDDPST 决定的。

ESP32-D2WD 芯片外接 PSRAM 软件配置注意事项是什么?

需要在 menuconfig 中使能

CPU frequece 240 Mhz和RTC clock 80 Mhz,具体配置如下:

menuconfig>Serial flasher config>Flash SPI Speed (80 Mhz)

Component config>CPU frequency (240 Mhz)

Component config>ESP32 specific>[*]Support for external, SPI-connected RAM

Component config>ESP32 specific>SPI RAM config>Set RAM clock speed (80 Mhz clock speed)

ESP32 芯片当 VDD 供电从 0 V 慢慢升到 3.3 V 时,芯片为何无法正常启动?

出现此问题是由于芯片上电时序不满足要求,时序要求当 VDD 达到 2.3 V 时,EN 电压不应超过 0.6 V。

但 VDD 上电时间过慢时,芯片 EN 端的 RC 电路将 EN 延时的功能就丧失了。

可以调整 RC 电路,增加电容,调整电阻,或是使用 Reset 芯片管控 EN 状态。

建议检测到供给 ESP32 的电压低于 2.3 V 时将 ESP32 的 EN 脚拉低。

ESP32 上电时序说明参见 《ESP32 技术规格书》。

使用 ESP32-WROOM-32D 模组,是否可以使用 GPIO12 用作其他功能?

GPIO12 为 Strapping 管脚,控制 SPI flash 的启动电压。ESP32-WROOM-32D 模组的 SPI flash 启动电压为 3.3 V,因此在上电启动时 GPIO12 需要拉低。

若需要使用 GPIO12 用作其他功能,请使用 esptool 工具通过 espefuse.py set_flash_voltage 3.3V 命令将 VDD_SDIO 固定为 3.3 V。

硬件上可以将 VDD_SDIO 直接连到 3.3 V 上,这样就不用再烧录 eFuse。

在量产阶段,也可以直接将 flash 下载工具里

config/esp32/utility.config文件下ESP32_EFUSE_CONFIG的默认配置选项修改为config_voltage = 3.3 V来下载固件。

ESP32-WROOM-32D 模组的外接 flash,是否可以不使用 GPIO6 ~ GPIO11 的接口?

ESP32 共有三组 SPI(SPI、HSPI 和 VSPI)接口,可以通过 SPI0/1 (HSPI/VSPI) 总线访问外部 flash。但接到其他脚(GPIO6 ~ GPIO11 以外的 GPIO)的外接 flash 不能跑程序,只能接收数据作存储。需要跑程序的 flash 只能接在 GPIO6 ~ GPIO11 接口上。

ESP32 芯片设计模组,PCB 板是否需要加屏蔽盖?

是否需要加屏蔽盖取决于具体的应用场景和要求。

在一些高要求的应用场景,例如无线通讯干扰环境较严峻、电磁兼容性 (EMC) 测试要求较高等情况下,加装屏蔽盖可以有效地减少外界干扰和 PCB 板上的互相干扰,提高系统的稳定性和可靠性。此时,屏蔽盖应该采用导电材料,并接地处理,以确保其有效性。

另一方面,如果应用场景较为简单,如无线通讯干扰较小,EMC 要求不高等情况下,加装屏蔽盖的效果可能不是很明显,且可能增加系统成本和复杂度。

如果板子还有其他信号干扰,比如 2G、3G、4G 或者 Wi-Fi、Bluetooth、Zigbee 等等建议加上屏蔽盖。

ESP32 的 I2S 的 CLK 管脚必须使用 GPIO0、GPIO1 或 GPIO3 吗?

MCLK 管脚必须使用 GPIO0、GPIO1 或 GPIO3 管脚。其他的时钟管脚可以使用任意的 GPIO。注意,由于 GPIO0 为 Strapping 管脚,一般不推荐用作其他功能。

ESP32-U4WDH 芯片是否支持外接 PSRAM 芯片?

ESP32-U4WDH 芯片支持外接 PSRAM 芯片,但仅支持乐鑫发布的 ESP-PSRAMXXH 芯片,不支持使用第三方 PSRAM 芯片。

硬件设计上,除了 CS 管脚外,其他所有管脚都可以与 Flash 复用,更多指南请参考 《ESP32 硬件设计指南》。

另外,PCB 设计时请注意 PSRAM 的 GND 到 ESP32-U4WDH 的 GND 要尽量短,否则可能会影响信号质量。

ESP32 芯片是否支持使用 SPI0/SPI1 接口外接 SD NAND flash 来存储程序固件(而不是使用默认的 NOR flash)?

ESP32 芯片不支持使用 SPI0/SPI1(连接程序 flash)接口来外接 SD NAND flash 芯片。

如果要存储外部数据,建议使用 ESP32 的 SPI2、SPI3 或 SDIO 接口来外接 NAND SD 芯片。

SPI2 和 SPI3 可以使用任意 GPIO,但 SDIO 接口则只能使用指定接口,详细说明请见 《ESP32 技术规格书》 中的 外设管脚分配 章节。

是否支持基于 ESP32-S3R8 芯片外挂第二个 PSRAM 芯片?

不支持。原因如下:

PSRAM 芯片与 MSPI 总线相连。MSPI 外设只有两个 CS 信号,一个与 flash 相连,另一个则与 PSRAM 相连。

CPU 通过 cache 和 MSPI 访问外部存储器。GPSPI 外设是不能被 cache 访问的。

能否提供 ESP32-S3-WROOM-1 模组的 3D 模型和 Footprint 文件?

可在 espressif/kicad-libraries 库中获取模组的 3D 模型和 Footprint 文件。

ESP32/ESP32-S2/ESP32-C3/ESP32-S3 是否支持单独给 RTC 电源域供电来保持芯片低功耗工作?

不支持。详细说明参见文档 RTC 时钟源(可选)(ESP32-C3) 中的硬件设计说明。

有哪些提高 EMC 性能的方法?

在硬件层面,可以采取以下措施来提高 PCB 板的 EMC 性能:

采用四层板设计的 EMC 性能优于两层板的硬件设计。

对电源电路增加滤波电路。

在天线电路中添加防静电或磁珠。

在 SPI Flash 电路上增加一个 0 欧姆串联电阻,以降低驱动电流,减少对射频的干扰,调整时序,更好地屏蔽干扰。

尽量保持 GND 完整。

更多硬件设计建议可参考 《ESP 硬件设计指南》。

ESP32-S3 U0TXD 为什么要预留 499 Ω 的电阻?

U0TXD 预留 499 Ω 电阻是用于抑制 80 MHz 谐波。详细信息请参考文档 UART。

如何在硬件上校准 ESP32-S3 ADC?

ESP32-S3 已经在芯片内部进行了 ADC 的硬件校准。ESP32-S3 ADC 对噪声敏感,可能导致 ADC 读数出现较大差异。根据使用场景,您可能需要将旁路电容(例如 100 nF 陶瓷电容)连接到使用的 ADC 输入焊盘,以最大限度地减小噪声。此外,还可以使用多重采样来进一步减轻噪声的影响。

如何基于 ESP32 系列芯片设计自动下载电路?

可以参考 ESP32-DevKitC 开发板原理图 中自动下载电路的硬件设计。

在 ESP8266 芯片上应该使用哪种晶振?

ESP8266 芯片需要使用 26 MHz 的晶振来启动芯片。选⽤的晶振⾃身精度需在 ±10 PPM。详情请参见 《ESP8266 硬件设计指南》。

ESP32-C2、ESP32-C3 和 ESP32-C6 芯片是否支持外接 PSRAM 芯片?

ESP32-C2、ESP32-C3 和 ESP32-C6 芯片均不支持外接 PSRAM 芯片。但 ESP32-C61 芯片将支持 2 MB PSRAM。

ESP32-C3 采用电池供电时,当供电电压逐渐下降,比如将电池放完电后再充电,ESP32-C3 可能会无法启动。此时,只能首先断开电池与 ESP32-C3 的连接,再重新连接充好电的电池,或者尝试在 3.3 V 引脚和 EN 引脚间连接一个稳压二极管才能让芯片正常启动,出现这种情况的根本原因是什么?有没有最佳的解决办法?

根本原因:ESP32-C3 芯片重新上电和复位时,CHIP_EN 管脚需要满足 ESP32-C3 芯片规格书 或 ESP32-C3 硬件设计指南 里的上电时序图要求和说明。如果电池放电和上电比较缓慢,ESP32-C3 可能无法充分复位,从而导致芯片部分单元处于不确定状态。

解决办法:目前,若使用电池供电或储能类应用系统,可以通过调整不同 RC 器件值、使用两个电阻分压控制,或使用一颗较为常见的复位芯片来解决此问题。有关 RC 器件值、相关电阻的详细信息,请参见 ESP32-C3 系列芯片硬件设计指南。

ESP32 系列模组上的九宫格 GND 网格是否需要铺铜?

模组上的九宫格 GND 网格建议铺铜。

为什么 ESP32 第一次上电无法启动,需要复位一次才能正常启动?

请检查 Boot 管脚是否连有过大的电容。

以太网 PHY 初始化失败,硬件层面可能是什么原因?

建议将 GPIO0 上的串联电阻换成 0 Ω 后再次尝试。

以太网 PHY 初始化成功,但是无法获取到 IP,硬件层面可能是什么原因?

请检查 GPIO0 上是否有较大的负载,可以去掉额外的电路再测试。

使用 ESP32 芯片设计的 PCB 无法正常连接到路由器,什么原因?

请在 XTAL_P 上串联 24 nH 电感。

请按照 此步骤 调节晶振两边的电容。

ESP32-C6 的 GPIO6(JTAG 管脚 MTCK)默认上电复位初始状态是输入使能和内部弱上拉电阻使能 (IE & WPU),是否可以通过烧写 eFuse 将其改为仅输入使能 (IE)?

可以。将 EFUSE DIS_PAD_JTAG 写为 1 后,GPIO6(JTAG 管脚 MTCK)的上电复位初始状态即改为输入使能 (IE),可参见 《ESP32-C6 技术规格书》 中的 2.2 管脚概述。

可通过 espefuse.py burn_efuse DIS_PAD_JTAG 指令来将 EFUSE DIS_PAD_JTAG 写为 1。

也可以在应用代码中添加如下代码来将 EFUSE DIS_PAD_JTAG 写为 1:

#include "esp_efuse.h" #include "esp_efuse_table.h" esp_efuse_write_field_bit(ESP_EFUSE_DIS_PAD_JTAG);

ESP32-H2 的 VBAT 引脚可否单独供电?

理论上支持 RTC 供电,但模组内部已连接 3.3V,该引脚实际不可用。

ESP32-P4 备用电池功能 (VBAT) 现在是否完全支持?

IDF 驱动里已有支持,参考

examples/lowpower/vbat示例。solution 下的文档过时,按最新 IDF 文档操作。VBAT 供电仅在 deep sleep 下切换,light sleep 不会切换到 VBAT 供电。此时必须外接 32.768 kHz 晶振。