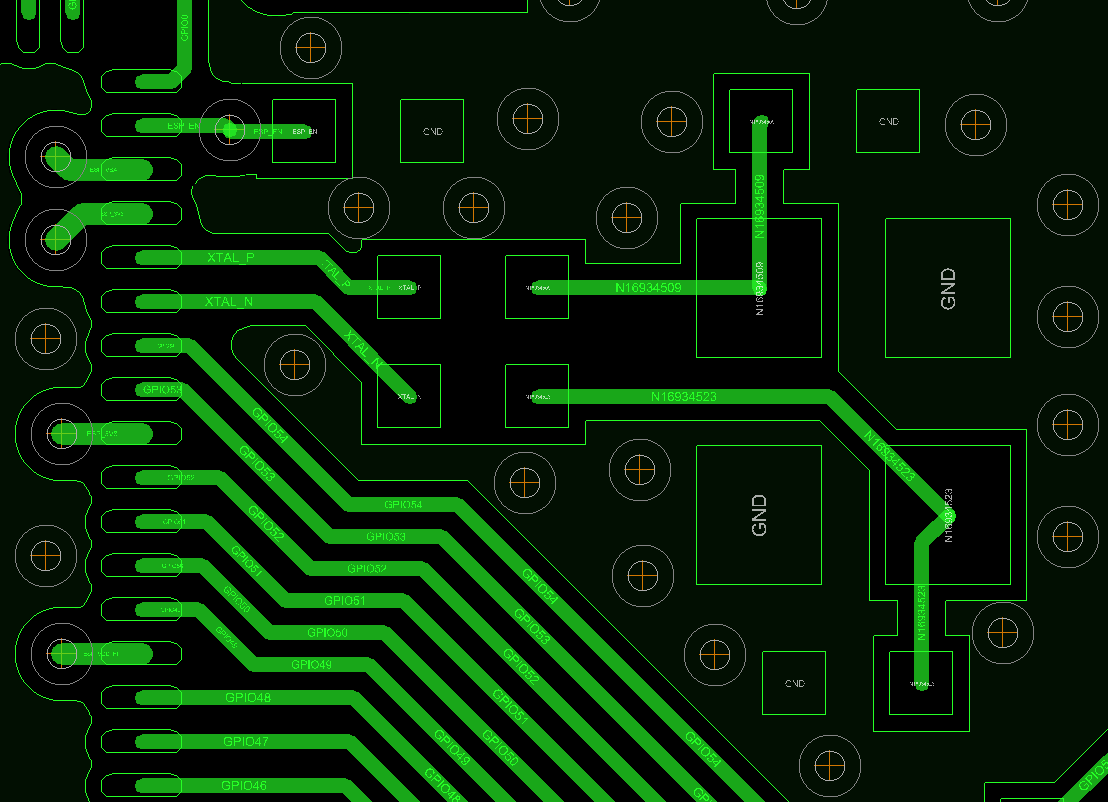

PCB 版图布局

本章节将以 ESP32-P4 开发板的 PCB 布局为例,介绍 ESP32-P4 系列芯片的 PCB 布局设计要点。

基于芯片的版图设计通用要点

考虑到高速信号线的通信质量和对射频模块的干扰问题,请至少采用四层板设计,即:

第一层(顶层),主要用于走信号线和摆件。

第二层(地层),不走信号线,保证一个完整的地平面。

第三层(电源线层),将电源走在该层;条件允许的话,将高速信号线走在该层并且保证参考平面完整。

第四层(底层),可走信号线。

电源走线通用要点

电源走线请尽量走在内层(非地层),通过过孔连接至芯片管脚处。电源走线周围注意包地良好。

3.3 V 总电源的走线的线宽建议至少 25 mil。

VDD_LP、VDD_IO_0、VDD_IO_4、VDD_IO_5、VDD_IO_6、VDD_BAT 和 VDD_ANA 各个管脚的电源走线建议至少 10 mil,这系列电源入口处请放置一个 10 μF 电容,然后在每个电源管脚上放置一个 0.1 μF 电容。

VDD_HP_0、VDD_HP_1、VDD_HP_2 与 VDD_HP_3 的总电源走线的线宽建议至少 20 mil,这系列电源入口处请放置一个 10 μF 电容,然后在每个电源管脚上放置一个 0.1 μF 电容。

VDD_LDO 和 VDD_DCDCC 因为电源电流较大,请在两个电源管脚附近放置一个 10 μF 电容,走线建议至少 20 mil。

每个系列的电源走线建议通过星型走线的方式分给各个电源管脚。

VDD_HP 电源的 DCDC 请靠近芯片放置,保证输入、输出和反馈回路尽可能小。因为 VDD_HP 电源默认由 ESP32-P4 内部完全控制,因此外部 DCDC 请靠近芯片放置,保证输入、输出和反馈回路尽可能小。

晶振

下图为 ESP32-P4 系列芯片晶振参考设计图。

ESP32-P4 系列芯片晶振设计

晶振设计应遵循以下规范:

需要保证晶振和芯片有一个完整的地平面。

晶振需离芯片时钟管脚稍远一些放置,防止晶振干扰到芯片。间距应至少为 4.5 mm。同时晶振走线须用地包起来周围密集地孔屏蔽隔离。

晶振的时钟走线不可打孔走线。

晶振上的串联元器件请靠近芯片放置。

晶振外接的对地调节电容请靠近晶振左右两侧摆放,不可直接连接在串联元器件上。电容尽量置于时钟走线连接末端,保证电容的地焊盘靠近晶振的地焊盘放置。

晶振下方都不能走高频数字信号,最好是晶振下方不走任何信号线。晶振时钟走线两侧的电源线上的过孔应尽可能地远离时钟走线放置,并使时钟走线两侧尽可能包地。

晶振为敏感器件,晶振周围不能放置磁感应器件,比如大电感等,保证晶振周围有干净的大面积地平面。

USB

USB 版图设计应遵循以下规范:

USB 线上预留的电阻和电容请靠近 ESP32-P4 放置。

USB 走线请按照差分走线,差分线阻抗控制标准是 90 Ω,误差不能大于 ±10%,保持平行等长。

USB 差分走线尽可能减少打孔换层,从而可以更好的做到阻抗的控制,避免信号的反射。如果必须打孔,请在每次打孔换层的地方加一对地孔回流。

USB 走线下方一定要有参考层(推荐用地层),且一定要保证参考层的连续性。

USB 走线两侧请注意包地处理。

SDIO

SDIO 版图设计应遵循以下规范:

SDIO 走线因为速率较高,需要尽量控制其寄生电容。

SDIO_CMD、SDIO_DATA0 ~ SDIO_DATA3 走线长度以 SDIO_CLK 走线长度为基准 ±50 mil,需要时绕蛇形线。

SDIO 走线请保证 50 Ω 单端阻抗控制,误差不能大于 ±10%。

从芯片 SDIO 管脚到对端 SDIO 接口的总长度越短越好,最好在 2000 mil 以内。

SDIO 走线要保证不跨平面。SDIO 走线下方一定要有要有参考层(推荐用地层),且一定要保证参考层的连续性。

SDIO_CLK 走线两侧请注意包地处理。

对于层数较多的 PCB 设计,建议 SDIO 走线在芯片引出后立即通过过孔引入内层,以降低高速信号线的干扰。同时,请在打孔换层的地方加一对地孔回流。

触摸传感器

ESP32-P4 提供多达 14 个电容式传感 IO,能够探测由手指或其他物品直接接触或接近而产生的电容差异。这种设计具有低噪声和高灵敏度的特点,可以用于支持使用相对较小的触摸板。矩阵按键的设计可以得到更多的触摸点。接近感应的设计可以检测到人体的接近。

图 ESP32-P4 典型的触摸传感器应用 为典型触摸传感应用。

ESP32-P4 典型的触摸传感器应用

为防止电容耦合和其他电干扰影响触摸传感系统的灵敏度,需要考虑以下因素:

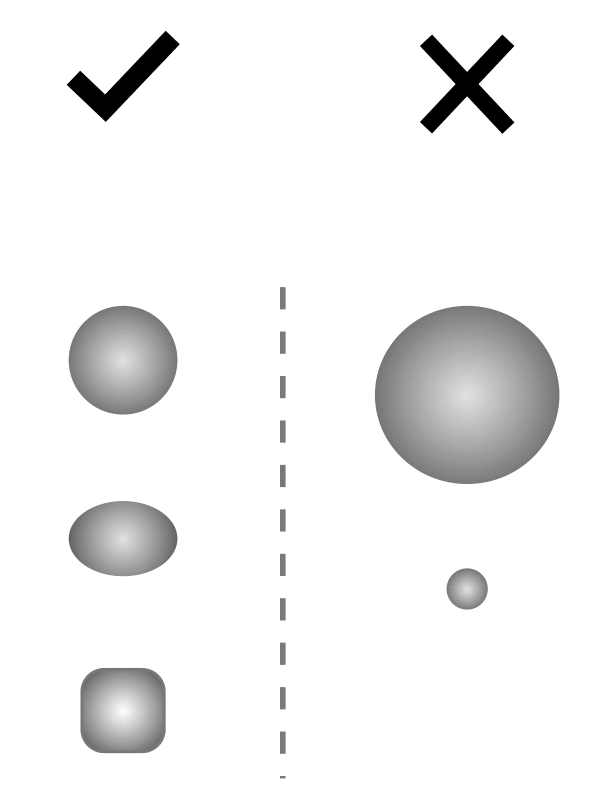

电极图形

适当大小和形状的电极有助于提高系统灵敏度。常见的有圆形、椭圆形和形状类似人的指尖的电极。过大或形状不规则的电极可能导致附近电极发生错误响应。

图 ESP32-P4 电极图形要求 所示为适当以及不适当大小和形状的电极。注意图中未按照实际比例绘制,建议用指尖作为参考。

ESP32-P4 电极图形要求

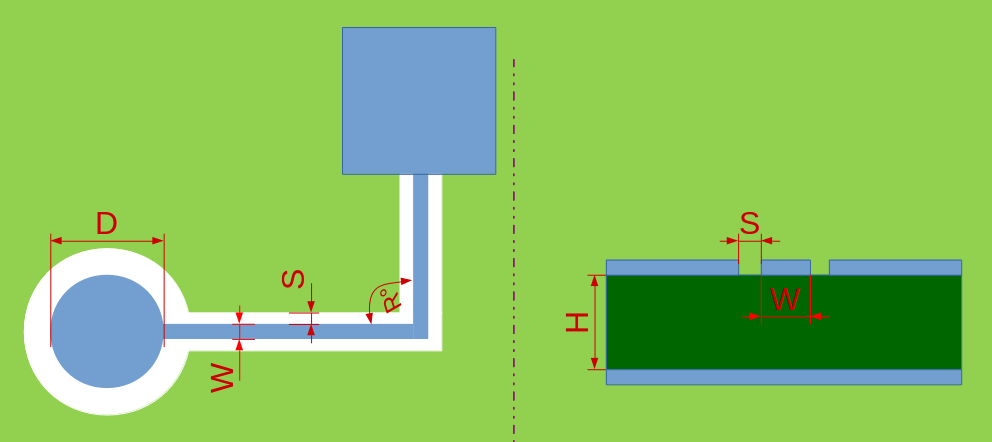

PCB 布局

图 ESP32-P4 传感器布局布线 为传感器布线布局,具体的走线注意事项如下:

走线长度请尽量短,建议不超过 300 mm。

走线宽度 (W) 不能大于 0.18 mm (7 mil)。

走线夹角 (R) 不应小于 90°。

走线离地间隙 (S) 范围 0.5 mm 到 1 mm。

触摸电极直径 (D) 范围 8 mm 到 15 mm。

触摸电极和走线应被栅格地围绕。

触摸传感器电路注意远离射频天线电路,并注意隔离。

ESP32-P4 传感器布局布线

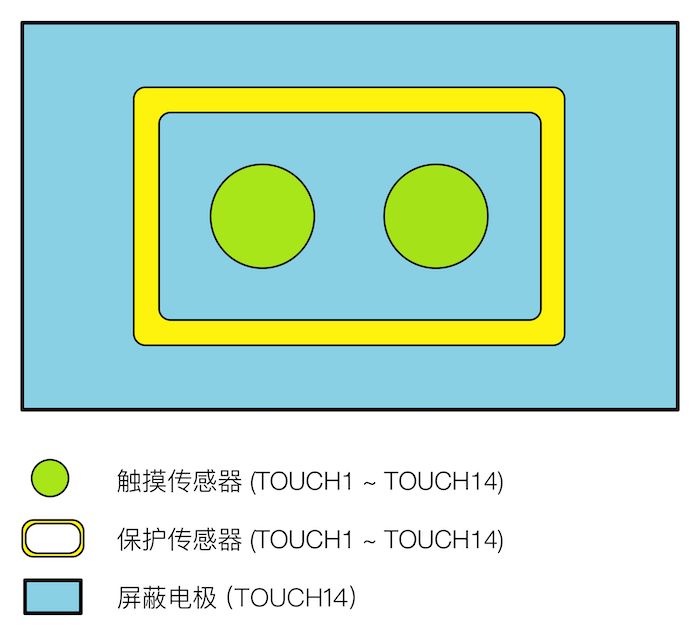

防水和接近传感器布局

ESP32-P4 新增硬件防水和接近传感器功能,图 ESP32-P4 防水和接近传感器参考布局 为防水和接近传感器参考的布局。

ESP32-P4 防水和接近传感器参考布局

为更好实现上述功能,请注意以下事项:

屏蔽电极的宽度建议 2 cm。

顶层填充网格,走线宽度为 7 mil,网格宽度为 45 mil(25% 填充),填充的网格与驱动屏蔽信号连接。

底层填充网格,走线宽度为 7 mil,网格宽度为 70 mil(17% 填充),填充的网格与驱动屏蔽信号连接。

建议保护传感器应为弯曲边缘的矩形,包围其他所有传感器。

保护传感器宽度建议为 2 mm。

保护传感器与屏蔽传感器宽度间隙建议为 1 mm。

接近传感器的感应距离与接近传感器的面积成正比,但增大感应面积也会带来更大噪声,需实际测试。

接近传感器形状建议为闭合环状。宽度建议为 1.5 mm。

备注

更多关于触摸传感器的硬件设计可查看 触摸传感器应用方案简介。

MIPI

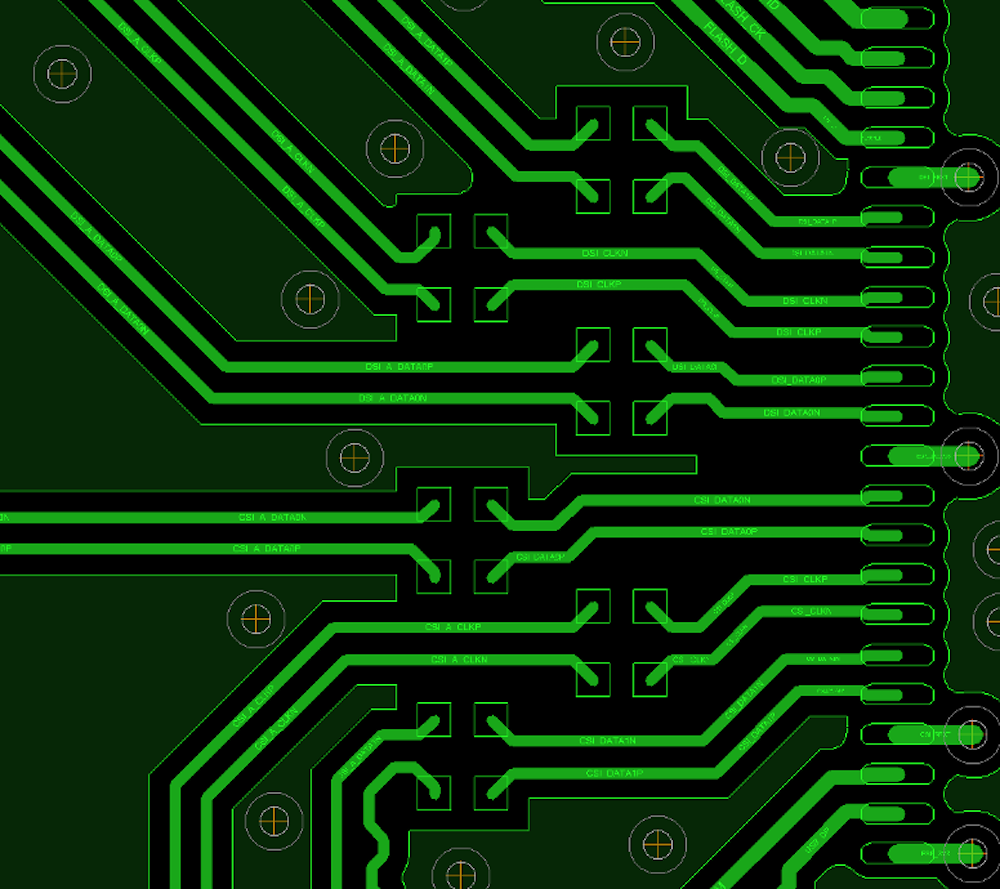

ESP32-P4 系列芯片 MIPI 版图设计

MIPI 版图设计应遵循以下规范:

MIPI 走线因为速率较高,需要尽量控制其寄生电容。

MIPI 的差分线阻抗控制标准是 100 Ω,误差不能大于 ±10%。

MIPI 线始终保持等长和等距;MIPI 线对之间的长度误差要控制在 10 mil 以内,线对与线对之间的长度误差控制在 30 mil 以内,需要时绕蛇形线。

MIPI 线对之间建议包地隔离,如果没有办法包地,MIPI 线对之间要保持至少 2W 以上的间距,其中 W 为 MIPI 线宽。MIPI CLK 走线请包地处理。

MIPI 信号线应远离其它高速、高频信号(并行数据线、时钟线等),至少保持 3W 以上的距离且绝不能平行走线,对开关电源这一类的干扰源更应远离。

MIPI 信号线下方一定要有参考层(推荐用地层),且一定要保证参考层的连续性。

对于层数较多的 PCB 设计,建议 MIPI 走线在芯片引出后立即通过过孔引入内层,以降低高速信号线的干扰。同时,请在打孔换层的地方加一对地孔回流。