原理图设计

概述

ESP32-P4 系列芯片的核心电路只需要 40 个左右的电阻电容电感和 1 个无源晶振,以及 1 个 SPI flash, 1 个 DCDC。为了能够更好地保证 ESP32-P4 系列芯片的工作性能,本章将详细介绍 ESP32-P4 系列芯片的原理图设计。

下图所示为 ESP32-P4 的核心电路参考设计,可以将它作为原理图设计的基础。

注意

对于新设计,请参考芯片版本 v3.0 及之后版本的原理图。

ESP32-P4 参考设计原理图(芯片版本 v3.0 及之后版本)

ESP32-P4 参考设计原理图(芯片版本 v1.0 和 v1.3)

重要

芯片版本 v1.0/v1.3 (不推荐用于新设计)与 v3.0 及之后版本 之间的主要差异在于管脚 54 的定义,DP 管脚上的 1 MΩ 电阻,DCDC 电路中的两个 499 kΩ 电阻及一个 22 pF 电容。相关差异的详细说明请参见后续章节。

在芯片版本 v3.0 及之后版本 中,ESP32-P4 的管脚 54 定义为 VDD_HP_1;而在芯片版本 v1.0 和 v1.3 中,该管脚定义为 NC。

ESP32-P4 芯片版本信息及其区分方式见 ESP32-P4 系列芯片勘误表。

ESP32-P4 系列芯片的核心电路图的设计有以下重要组成部分:

下文将分别对这些部分进行描述。

电源

电源电路设计的通用要点有:

使用单电源供电时,建议供给 ESP32-P4 的电源电压为 3.3 V。

ESP32-P4 的基本供电电流至少为 380 mA(含 flash 和 PSRAM),各个外设的供电电流请参考 HP/LP IO 电源, MIPI PHY 电源 和 USB PHY 电源。请根据具体应用选择合适的电源芯片。

建议在各个总电源入口处添加 10 μF 电容。

电源管理如图 ESP32-P4 系列芯片电源管理 所示。

ESP32-P4 系列芯片电源管理

有关电源管脚的更多信息,请查看 ESP32-P4 系列芯片技术规格书 > 章节 电源。

HP/LP IO 电源

管脚序号 |

管脚名称 |

管脚方向 |

电压范围 (V) |

最大拉电流 (mA) |

IO 管脚 |

管脚处电容 (μF) |

|---|---|---|---|---|---|---|

9 |

VDD_LP |

输入 |

3.0 ~ 3.6 |

100 |

LP IO |

0.1 |

21 |

VDD_IO_0 |

输入 |

1.65 ~ 3.6 |

100 |

HP IO |

0.1 |

62 |

VDD_IO_4 |

输入 |

1.65 ~ 3.6 |

100 |

HP IO |

0.1 |

85 |

VDD_IO_5 1 |

输入 |

1.65 ~ 3.6 |

100 |

HP IO |

0.1 |

96 |

VDD_IO_6 |

输入 |

1.65 ~ 3.6 |

100 |

HP IO |

0.1 |

MIPI PHY 电源

ESP32-P4 的管脚 VDD_MIPI_DPHY 为 MIPI PHY 电源管脚,工作电压范围为 2.25 V ~ 2.75 V,最大电流功耗为 50 mA。推荐使用内部电压稳压器供电,建议在电路中靠近 VDD_MIPI_DPHY 管脚处添加 10 nF + 0.1 μF + 1 μF。

如果不需要 MIPI 功能,管脚 VDD_MIPI_DPHY 可以悬空。

注意

MIPI 信号电平由 MIPI 协议规定,具体可以查阅 MIPI 协议相关文档,和 MIPI DPHY 电平是两个概念。摄像头/显示屏规格书中提到的 1.8 V/3.3 V 指的是除 MIPI 信号 (Data Lane & CLK) 之外的信号电平,如 MCLK 和 I2C 等。MIPI 信号电平由 ESP32-P4 内部 MIPI DPHY 自行处理,无需额外配置。

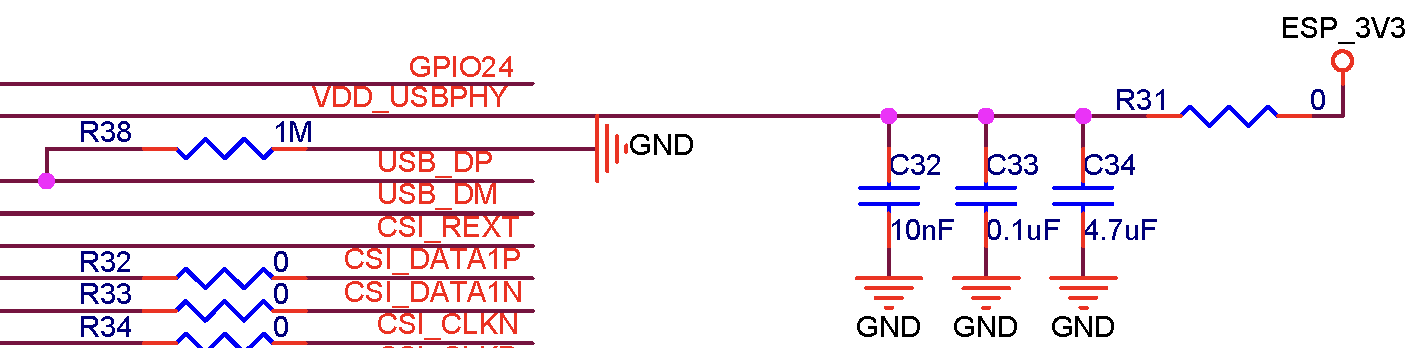

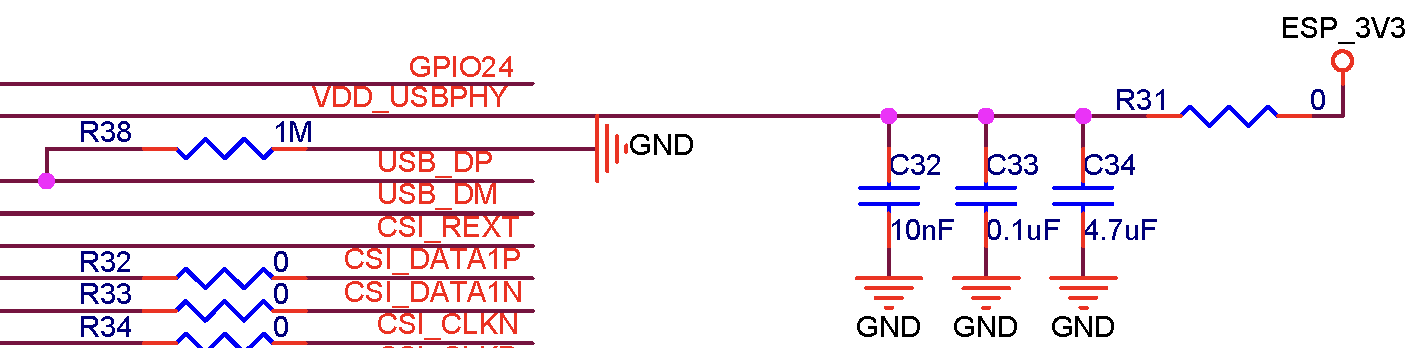

USB PHY 电源

ESP32-P4 的管脚 VDD_USBPHY 为 USB PHY 电源管脚,工作电压范围为 2.97 V ~ 3.63 V,最大电流功耗为 20 mA。建议在电路中靠近 VDD_USBPHY 电源管脚处添加 10 nF + 0.1 μF + 4.7 μF。

如果不需要使用 DP 和 DM,电源 VDD_USBPHY 可以悬空。

如果需要使用 DP 和 DM,在芯片版本 v1.0 和 v1.3(不推荐用于新设计)中,请注意电源 VDD_USBPHY 在低功耗模式下有漏电,因此建议添加一个 MOSFET 电路,从而在低功耗模式下可以完全关断该电源。验证阶段可以添加一个 0 Ω 串联电阻在 VDD_USBPHY 上。

VDD_USBPHY 电路参考设计(芯片版本 v1.0 和 v1.3)

在芯片版本 v3.0 和之后版本中,该问题已经被修复,可以保留 0 Ω 串联电阻用于兼容设计。

Flash 和 PSRAM IO 电源

ESP32-P4 的管脚 VDD_FLASHIO 为 FLASH IO 电源管脚,工作电压范围为 1.65 V ~ 3.6 V。该电源由内部电压稳压器输出 VDDO_FLASH 提供,建议在电路中靠近 VDD_FLASHIO 电源管脚处添加 0.1 μF + 1 μF。

管脚 VDD_PSRAM_0 和 VDD_PSRAM_1 为 PSRAM IO 电源管脚,工作电压范围为 1.65 V ~ 1.95 V。该电源由内部电压稳压器输出 VDDO_PSRAM 提供,建议在电路中靠近 VDD_PSRAM_0 和VDD_PSRAM_1 电源管脚处添加 0.1 μF + 1 μF。

模拟电源

ESP32-P4 的管脚 VDD_ANA 为模拟电源管脚,工作电压范围为 3.0 V ~ 3.6 V。建议在电路中靠近 VDD_ANA 电源管脚处添加 0.1 μF。管脚 VDD_BAT 为模拟电源管脚,工作电压范围为 2.5 V ~ 3.6 V,建议在电路中靠近 VDD_ANA 电源管脚处添加 0.1 μF + 10 μF。

VDD_BAT 电源管脚不可悬空,可外接电池,请参考 ESP32-P4 备用电池供电方案。

数字电源

ESP32-P4 的管脚 VDD_HP_0、管脚 VDD_HP_1、管脚 VDD_HP_2 和管脚 VDD_HP_3 为数字电源管脚,工作电压范围为 0.99 V ~ 1.3 V。该电源由外部 DCDC 输出 ESP_VDD_HP 提供,建议在总电源处添加 10 uF,在各个电源管脚处添加 0.1 μF。

内部电压稳压器和外部 DCDC

ESP32-P4 的管脚 VDD_LDO 为内部电压稳压器提供电源,工作电压范围为 3.0 V ~ 3.6 V。管脚 VDD_DCDCC 为 DCDC 控制部分提供电源,工作电压范围为 3.0 V ~ 3.6 V。因为管脚电流较大,请在 VDD_LDO 和 VDD_DCDCC 的电源走线上放置一个 10 μF 电容,再在各个管脚处添加 0.1 μF。

内部电压稳压器输出 VDDO_FLASH 给外部 flash 供电,默认输出 3.3 V 电压,可以通过烧写 EFUSE_0PXA_TIEH_SEL_0 使 VDDO_FLASH 输出 1.8 V。

备注

建议在使用 1.8 V SPI flash 时,在确认 VDDO_FLASH 输出电压已正确配置为 1.8 V 之前,先断开 VDDO_FLASH 与 SPI flash 的电源连接,以避免因供电电压过高而导致 1.8 V flash 损坏。

若该方案用于量产,请联系商务。

VDDO_FLASH 电源 |

EFUSE_0PXA_TIEH_SEL_0 |

电压 |

|---|---|---|

flash 稳压器 |

0 |

3.3 V |

2 |

1.8 V |

内部电压稳压器输出 VDDO_PSRAM 给内部 PSRAM 供电,输出典型值为 1.9 V 电压,需要软件配置,默认输出 0。

内部电压稳压器输出 VDDO_3/4 给外设供电,最大输出电流50 mA,输出电压范围为 0.5 V ~ 2.7 V/3.3 V,需要软件配置,默认输出 0。

软件配置请参考 低压差线性稳压器 (LDO)。

建议在电路中靠近 VDDO_FLASH、VDDO_PSRAM、VDDO_3/4 电源管脚处添加 1 μF。

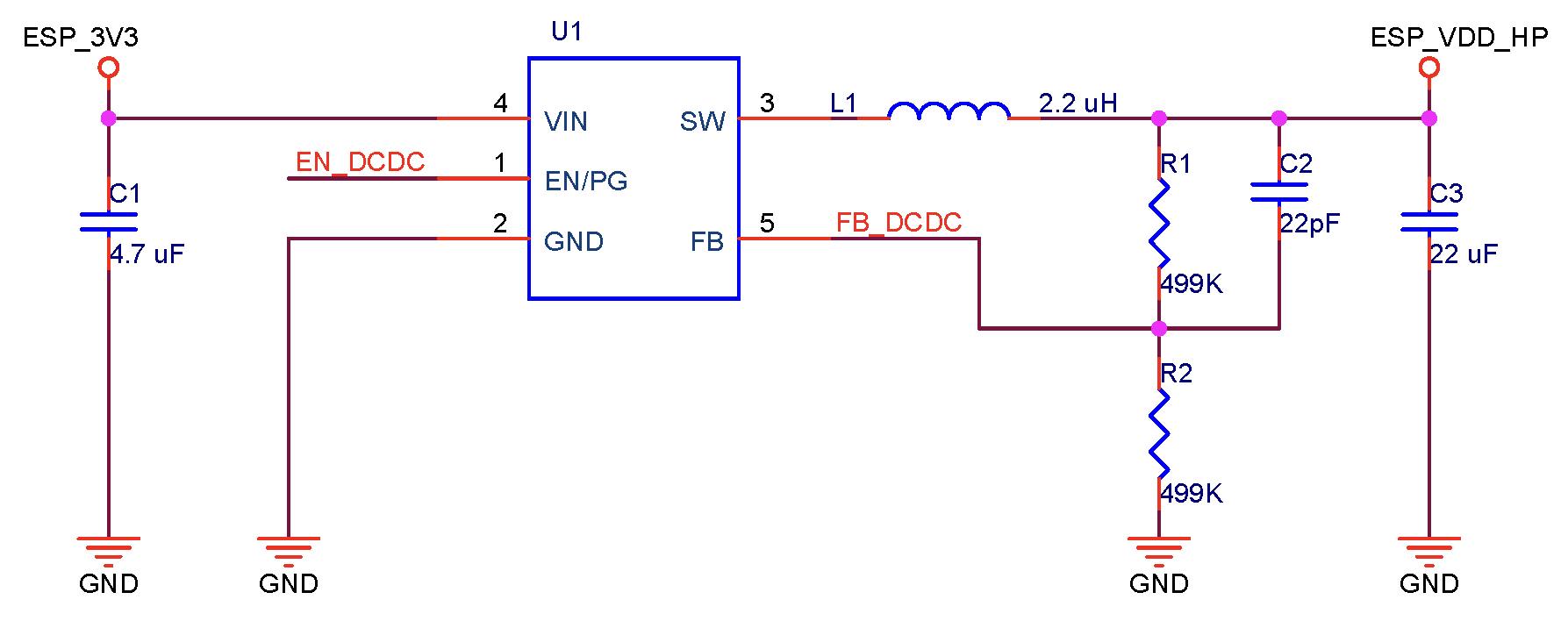

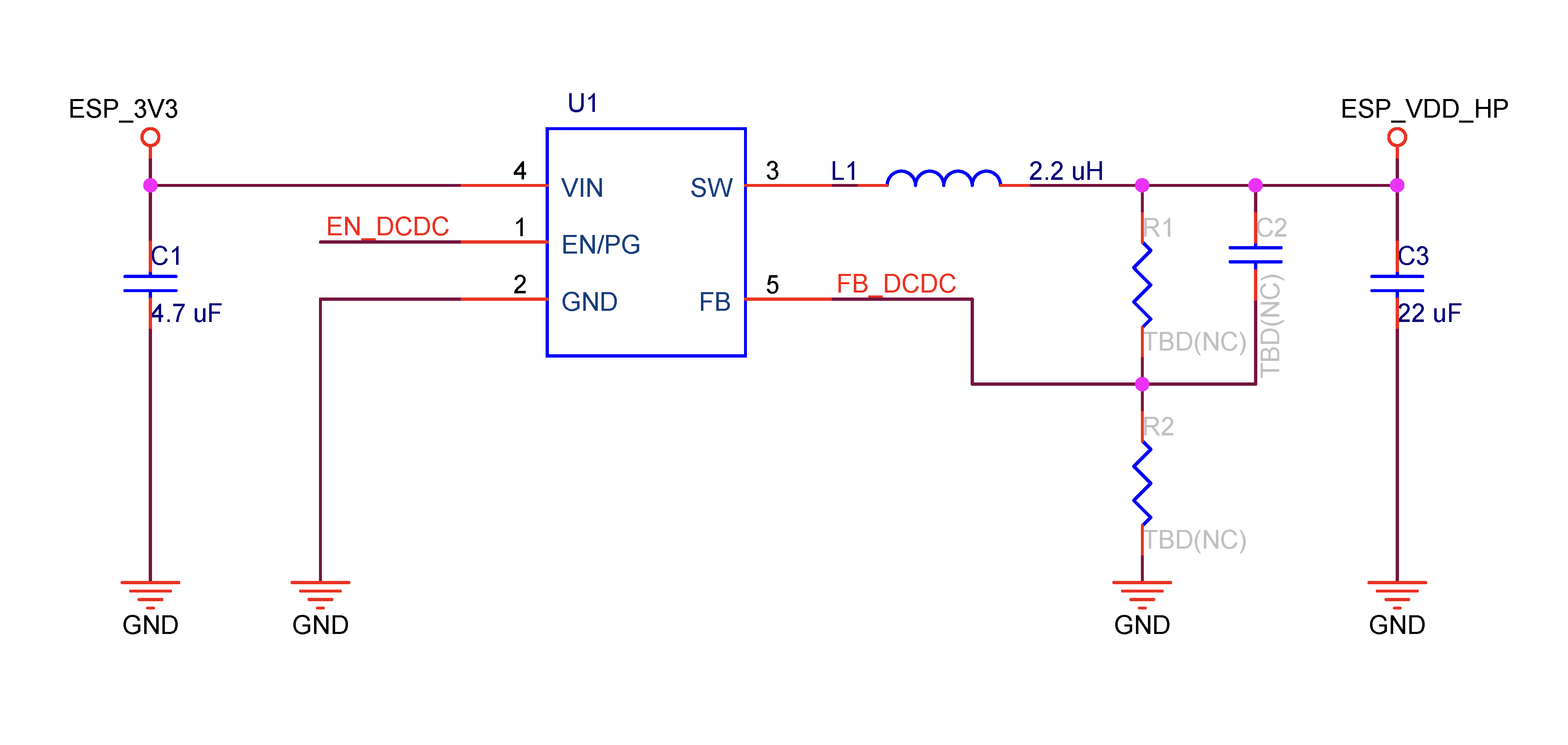

VDD_HP_0/1/2/3 系列电源由外部 DCDC 供电,其中:

外部 DCDC 的输入和 VDD_DCDCC 电源一致。

管脚 EN_DCDC 为外部 DCDC 的使能管脚。在下载模式和没有固件的情况下,EN_DCDC 电压为 0。正常启动固件后,EN_DCDC 由内部控制。在下载模式下,EN_DCDC 电压为 0。在睡眠模式下,可以通过管脚 EN_DCDC 关闭该系列的电源从而降低功耗。

管脚 FB_DCDC 为外部 DCDC 的反馈管脚。

管脚 EN_DCDC 与 FB_DCDC 默认由 ESP32-P4 内部电路全权控制,请务必将其分别连接至外部 DCDC 的 EN 与 FB 管脚,同时确保 DCDC 紧靠 ESP32-P4 放置。使用芯片版本 v1.0 和 v1.3(不推荐用于新设计)布局时必须预留反馈电阻与反馈电容的焊盘位置但无需上件,使用芯片版本 v3.0 和之后版本布局时则需要上件反馈电阻和反馈电容。

请使用验证过的 DCDC 型号:ETA3485/SY8088/RY3420/TLV62569。输入、输出和电感参数请按照具体的规格书设计,下图为 TLV62569 的电路设计。

TLV62569 电路参考设计(芯片版本 v3.0 及之后版本)

TLV62569 电路参考设计(芯片版本 v1.0 和 v1.3)

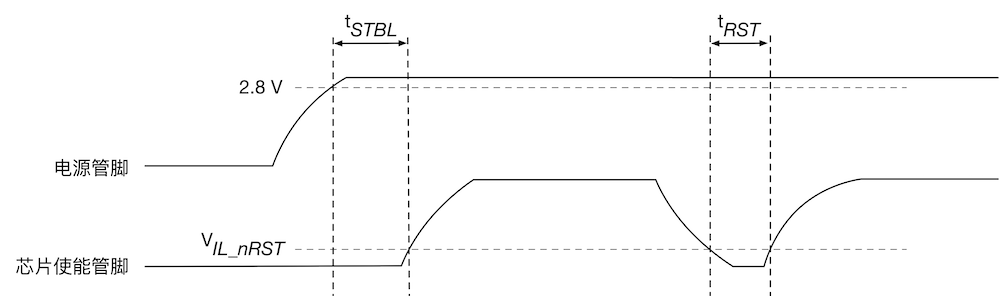

上电时序与复位

ESP32-P4 的 CHIP_PU 管脚为高电平时使能芯片,为低电平时复位芯片。

当 ESP32-P4 使用 3.3 V 系统电源供电时,电源轨需要一些时间才能稳定,之后才能拉高 CHIP_PU,激活芯片。因此,CHIP_PU 管脚上电要晚于系统电源 3.3 V 上电。

复位芯片时,复位电压 VIL_nRST 范围应为 (–0.3 ~ 0.25 × VDD_BAT) V。为防止外界干扰引起重启,CHIP_PU 管脚引线需尽量短一些。

图 ESP32-P4 系列芯片上电和复位时序图 为 ESP32-P4 系列芯片的上电、复位时序图。

ESP32-P4 系列芯片上电和复位时序图

上电和复位时序参数说明见表 上电和复位时序参数说明。

参数 |

说明 |

最小值 (µs) |

|---|---|---|

tSTBL |

CHIP_PU 管脚上电晚于电源管脚上电的延时时间 |

50 |

tRST |

CHIP_PU 电平低于 VIL_nRST 从而复位芯片的时间 |

1000 |

注意

CHIP_PU 管脚不可浮空。

为确保芯片上电和复位时序正常,一般采用的方式是在 CHIP_PU 管脚处增加 RC 延迟电路。RC 通常建议为 R = 10 kΩ,C = 0.1 μF,但具体数值仍需根据实际的电源特性配合芯片的上电、复位时序进行调整。

如果应用中存在以下场景:

电源缓慢上升或下降,例如电池充电;

需要频繁上下电的操作;

供电电源不稳定,例如光伏发电等。

此时,仅仅通过 RC 电路不一定能满足时序要求,有概率会导致芯片无法进入正常的工作模式。此时,需要增加一些额外的电路设计,比如:

增加复位芯片或者看门狗芯片,通常阈值为 3.0 V 左右;

通过按键或主控实现复位等。

Flash 及 PSRAM

ESP32-P4 系列芯片需配合封装外 flash 一起使用,用于存储应用的固件和数据。ESP32-P4 支持以 SPI、Dual SPI、Quad SPI 等接口形式连接 flash,最大可支持 64 MB flash。

ESP32-P4 系列芯片内部封装了 OPI/HPI 1.8 V PSRAM,请注意 PSRAM 引脚并没有引出芯片。

下面的表格列出了 ESP32-P4 与封装外 flash 的管脚对应关系。请注意这些芯片管脚最多连接一个 flash。

ESP32-P4 |

封装外 Flash (Quad SPI) |

|---|---|

FLASH_CK |

CLK |

FLASH_CS |

CS# |

FLASH_D |

DI |

FLASH_Q |

DO |

FLASH_WP |

WP# |

FLASH_HOLD |

HOLD# |

请注意默认使用 VDDO_FLASH 输出电源作为 flash 的电源,默认使用 VDDO_PSRAM 输出电源作为 PSRAM 的电源。

当 VDDO_FLASH 为 3.3 V 输出模式的时候,VDD_LDO 需要考虑到 RVFB 的影响。比如在接 3.3 V flash 的情况下需满足以下条件:

其中,VDD_flash_min 为 flash 的最低工作电压,I_flash_max 为 flash 的最大工作电流,RVFB 是 3.3 V 模式导通电阻。

注意

建议 SPI flash 通信线上预留 0 Ω 串联电阻,以便在需要时进行灵活调整,实现降低驱动电流、减小对射频的干扰、调节时序、提升抗干扰能力等功能。

请在 FLASH_CS 管脚处添加上拉电阻。

建议在 flash 电源处添加 0.1 μF 电容。

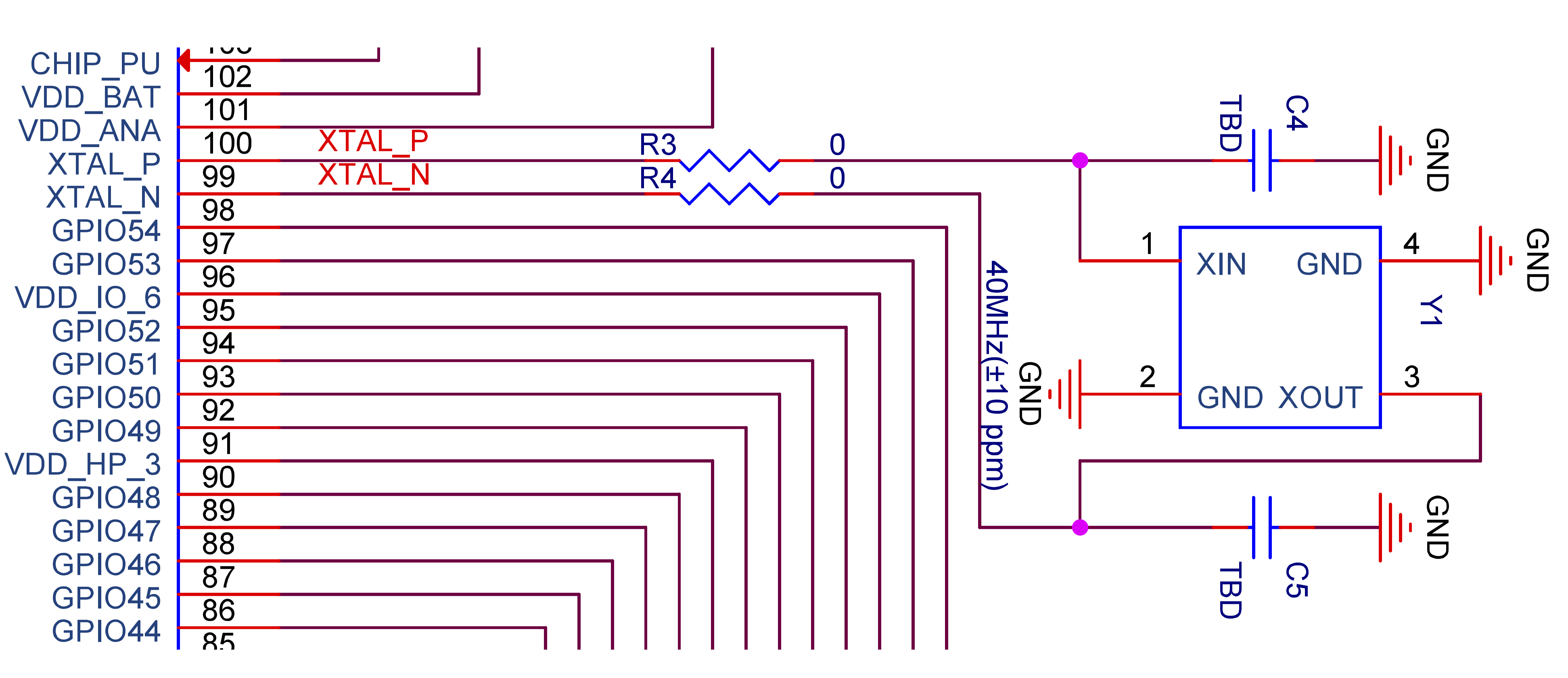

时钟源

ESP32-P4 外部可以有两个时钟源:

外置主晶振时钟源(必选)

目前 ESP32-P4 系列芯片固件仅支持 40 MHz 晶振。

ESP32-P4 的无源晶振部分电路如图 ESP32-P4 系列芯片无源晶振电路图。注意,选用的无源晶振自身精度需在 ±10 ppm。

ESP32-P4 系列芯片无源晶振电路图

外部匹配电容 C4 和 C5 的初始值可参考以下公式来决定:

其中 CL (负载电容)的值可查看所选择晶振的规格书,Cstray 的值为 PCB 的寄生电容。C4 和 C5 的最终值需要通过对系统测试后进行调节确定。

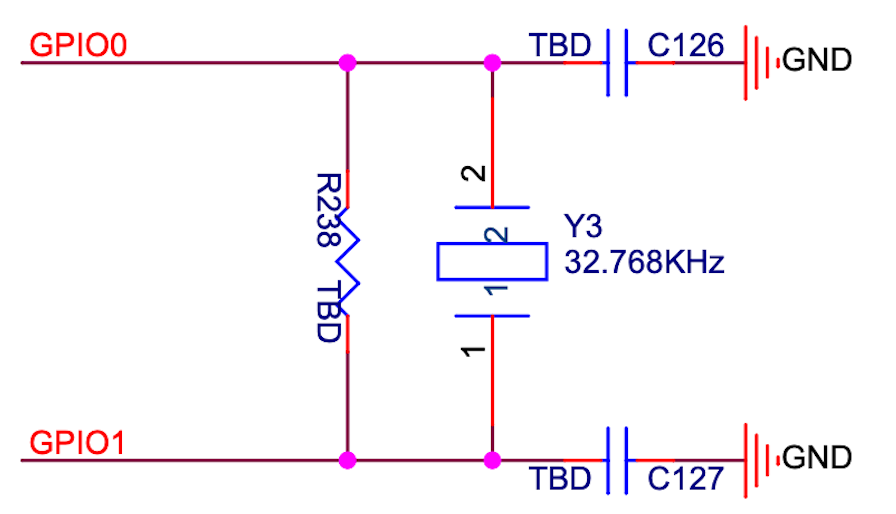

RTC 时钟源(可选)

ESP32-P4 支持外置 32.768 kHz 的无源晶振作为 RTC 时钟。使用外部 RTC 时钟源是为了使时间更准确,从而降低平均功耗,但对于功能没有任何影响。

外置 32.768 kHz 无源晶振的电路如图 ESP32-P4 系列芯片外置 32.768 kHz 无源晶振电路图 所示。

ESP32-P4 系列芯片外置 32.768 kHz 无源晶振电路图

请注意 32.768 kHz 晶振选择要求:

等效内阻 (ESR) ≤ 70 kΩ。

两端负载电容值根据晶振的规格要求进行配置。

并联电阻 R 用于偏置晶振电路,电阻值要求 5 MΩ < R ≤ 10 MΩ。该电阻一般无需上件。

如果不需要该 RTC 时钟源,则 32.768 kHz 晶振的管脚也可配置为 GPIO 使用。

UART

ESP32-P4 有 5 个 UART 接口,即 UART0 ~ UART4,5 个 UART 均支持 CTS 和 RTS 信号的硬件流控以及软件流控(XON 和 XOFF)。ESP32-P4 还有 1 个 LP UART,LP UART 支持 CTS 和 RTS 信号的硬件流控以及软件流控(XON 和 XOFF)。

UART0_TXD 和 UART0_RXD 默认为 GPIO37 和 GPIO38,其他 UART0 信号可以通过软件配置到任意空闲 GPIO 管脚上。LP UART TXD 和 LP UART RXD 默认为 LP GPIO14 和 LP GPIO15,其他 LP UART 信号可以通过软件配置到任意空闲 LP GPIO 管脚上。

UART0 通常作为下载和 log 打印的串口,关于如何使用 UART0 进行下载,请参考章节 下载指导。

推荐使用 UART1 ~ UART4 作为通信的串口。

SPI

在使用 SPI 功能时,为了提高 EMC 性能,请在 SPI_CLK 线上添加串联电阻(或磁珠)以及对地电容。如果空间允许,建议在其他 SPI 线上也添加串联电阻和对地电容。另外,请确保 RC/LC 器件靠近芯片或模组的管脚放置。

Strapping 管脚

芯片每次上电或复位时,都需要一些初始配置参数,如加载芯片的启动模式等。这些参数通过 strapping 管脚控制。复位放开后,strapping 管脚和普通 IO 管脚功能相同。

GPIO34、GPIO35、GPIO36、GPIO37、GPIO38 为 strapping 管脚。

所有的 strapping 管脚信息,可参考 ESP32-P4 系列芯片技术规格书 > 章节 启动配置项。下面主要介绍和启动模式有关的 strapping 管脚信息。

芯片复位释放后,GPIO35、 GPIO36、 GPIO37 和 GPIO38 共同决定启动模式,详见表 芯片启动模式控制。

启动模式 |

GPIO35 |

GPIO36 |

GPIO37 |

GPIO38 |

|---|---|---|---|---|

SPI Boot 模式(默认) |

1 |

任意值 |

任意值 |

任意值 |

Joint Download 模式 2 |

0 |

1 |

任意值 |

任意值 |

- 2

Joint Download 模式下支持以下下载模式:

USB Download Boot:

USB-Serial-JTAG Download Boot

USB 2.0 OTG Download Boot

UART Download Boot

SPI Slave Download Boot

Strapping 管脚的时序参数包括 建立时间 和 保持时间。更多信息,详见图 Strapping 管脚的时序参数图 和表 Strapping 管脚的时序参数说明。

参数 |

说明 |

最小值 (ms) |

|---|---|---|

tSU |

建立时间,即拉高 CHIP_PU 激活芯片前,电源轨达到稳定所需的时间 |

0 |

tH |

保持时间,即 CHIP_PU 已拉高、strapping 管脚变为普通 IO 管脚开始工作前,可读取 strapping 管脚值的时间 |

3 |

注意

建议在 GPIO35 管脚处预留上拉电阻。

建议不要在 GPIO35 管脚处添加较大的电容,可能会导致进入下载模式。

GPIO

ESP32-P4 系列芯片通过 IO MUX 表格或者 GPIO 交换矩阵来配置 GPIO。IO MUX 是默认的外设管脚配置(详见 ESP32-P4 系列芯片技术规格书 > 附录 ESP32-P4 管脚总览),GPIO 交换矩阵用于将可以配置的外设信号传输至 GPIO 管脚。更多关于 IO MUX 和 GPIO 交换矩阵的信息,请参考 ESP32-P4 技术参考手册 > 章节 IO MUX 和 GPIO 交换矩阵。

部分外设的 GPIO 管脚是固定的,部分是可以任意配置的,具体信息请参考 ESP32-P4 系列芯片技术规格书 > 章节 外设。

使用 GPIO 时,请注意:

Strapping 管脚的上电状态。

请注意 GPIO 复位后的默认配置,详见表 IO 默认管脚配置。建议对处于高阻态的管脚配置上拉或下拉,或在软件初始化时开启管脚自带的上下拉,以避免不必要的耗电。

Deep-sleep 模式下只能控制电源域为 VDD_LP 的 GPIO。

仅用电池供电时只能控制电源域为 VDD_BAT 的 GPIO。

管脚序号 |

管脚名称 |

供电管脚 |

复位时 |

复位后 |

|---|---|---|---|---|

1 |

GPIO1 |

VDD_LP/VDD_BAT |

– |

– |

2 |

GPIO2 |

VDD_LP/VDD_BAT |

– |

IE, WPU |

3 |

GPIO3 |

VDD_LP/VDD_BAT |

– |

IE |

4 |

GPIO4 |

VDD_LP |

– |

IE |

5 |

GPIO5 |

VDD_LP |

– |

– |

6 |

GPIO6 |

VDD_LP |

– |

– |

7 |

GPIO7 |

VDD_LP |

– |

– |

8 |

GPIO8 |

VDD_LP |

– |

– |

10 |

GPIO9 |

VDD_LP |

– |

– |

11 |

GPIO10 |

VDD_LP |

– |

– |

12 |

GPIO11 |

VDD_LP |

– |

– |

13 |

GPIO12 |

VDD_LP |

– |

– |

14 |

GPIO13 |

VDD_LP |

– |

– |

15 |

GPIO14 |

VDD_LP |

– |

– |

16 |

GPIO15 |

VDD_LP |

– |

– |

17 |

GPIO16 |

VDD_IO_0 |

– |

– |

18 |

GPIO17 |

VDD_IO_0 |

– |

– |

19 |

GPIO18 |

VDD_IO_0 |

– |

– |

20 |

GPIO19 |

VDD_IO_0 |

– |

– |

22 |

GPIO20 |

VDD_IO_0 |

– |

– |

23 |

GPIO21 |

VDD_IO_0 |

– |

– |

24 |

GPIO22 |

VDD_IO_0 |

– |

– |

25 |

GPIO23 |

VDD_IO_0 |

– |

– |

52 |

GPIO24 |

VDD_IO_4 |

– |

– |

53 |

GPIO25 |

VDD_IO_4 |

– |

IE, USB_PU |

55 |

GPIO26 |

VDD_IO_4 |

– |

– |

56 |

GPIO27 |

VDD_IO_4 |

– |

– |

57 |

GPIO28 |

VDD_IO_4 |

– |

– |

58 |

GPIO29 |

VDD_IO_4 |

– |

– |

60 |

GPIO30 |

VDD_IO_4 |

– |

– |

61 |

GPIO31 |

VDD_IO_4 |

– |

– |

63 |

GPIO32 |

VDD_IO_4 |

IE |

– |

64 |

GPIO33 |

VDD_IO_4 |

IE |

– |

65 |

GPIO34 |

VDD_IO_4 |

IE |

– |

66 |

GPIO35 |

VDD_IO_4 |

IE, WPU |

– |

68 |

GPIO36 |

VDD_IO_4 |

IE |

– |

69 |

GPIO37 |

VDD_IO_4 |

IE |

– |

70 |

GPIO38 |

VDD_IO_4 |

IE |

– |

80 |

GPIO39 |

VDD_IO_5 |

– |

– |

81 |

GPIO40 |

VDD_IO_5 |

– |

– |

82 |

GPIO41 |

VDD_IO_5 |

– |

– |

83 |

GPIO42 |

VDD_IO_5 |

– |

– |

84 |

GPIO43 |

VDD_IO_5 |

– |

– |

86 |

GPIO44 |

VDD_IO_5 |

– |

– |

87 |

GPIO45 |

VDD_IO_5 |

– |

– |

88 |

GPIO46 |

VDD_IO_5 |

– |

– |

89 |

GPIO47 |

VDD_IO_5 |

– |

– |

90 |

GPIO48 |

VDD_IO_5 |

– |

– |

92 |

GPIO49 |

VDD_IO_6 |

– |

– |

93 |

GPIO50 |

VDD_IO_6 |

– |

– |

94 |

GPIO51 |

VDD_IO_6 |

– |

– |

95 |

GPIO52 |

VDD_IO_6 |

– |

– |

97 |

GPIO53 |

VDD_IO_6 |

– |

– |

98 |

GPIO54 |

VDD_IO_6 |

– |

– |

104 |

GPIO0 |

VDD_LP/VDD_BAT |

– |

– |

ADC

使用 ADC 功能时,请靠近管脚添加 0.1 μF 的对地滤波电容,精度会更准确一些。

ADC 通道信号 |

管脚名称 |

|---|---|

ADC1_CHANNEL0 |

GPIO16 |

ADC1_CHANNEL1 |

GPIO17 |

ADC1_CHANNEL2 |

GPIO18 |

ADC1_CHANNEL3 |

GPIO19 |

ADC1_CHANNEL4 |

GPIO20 |

ADC1_CHANNEL5 |

GPIO21 |

ADC1_CHANNEL6 |

GPIO22 |

ADC1_CHANNEL7 |

GPIO23 |

ADC2_CHANNEL0 |

GPIO49 |

ADC2_CHANNEL1 |

GPIO50 |

ADC2_CHANNEL2 |

GPIO51 |

ADC2_CHANNEL3 |

GPIO52 |

ADC2_CHANNEL4 |

GPIO53 |

ADC2_CHANNEL5 |

GPIO54 |

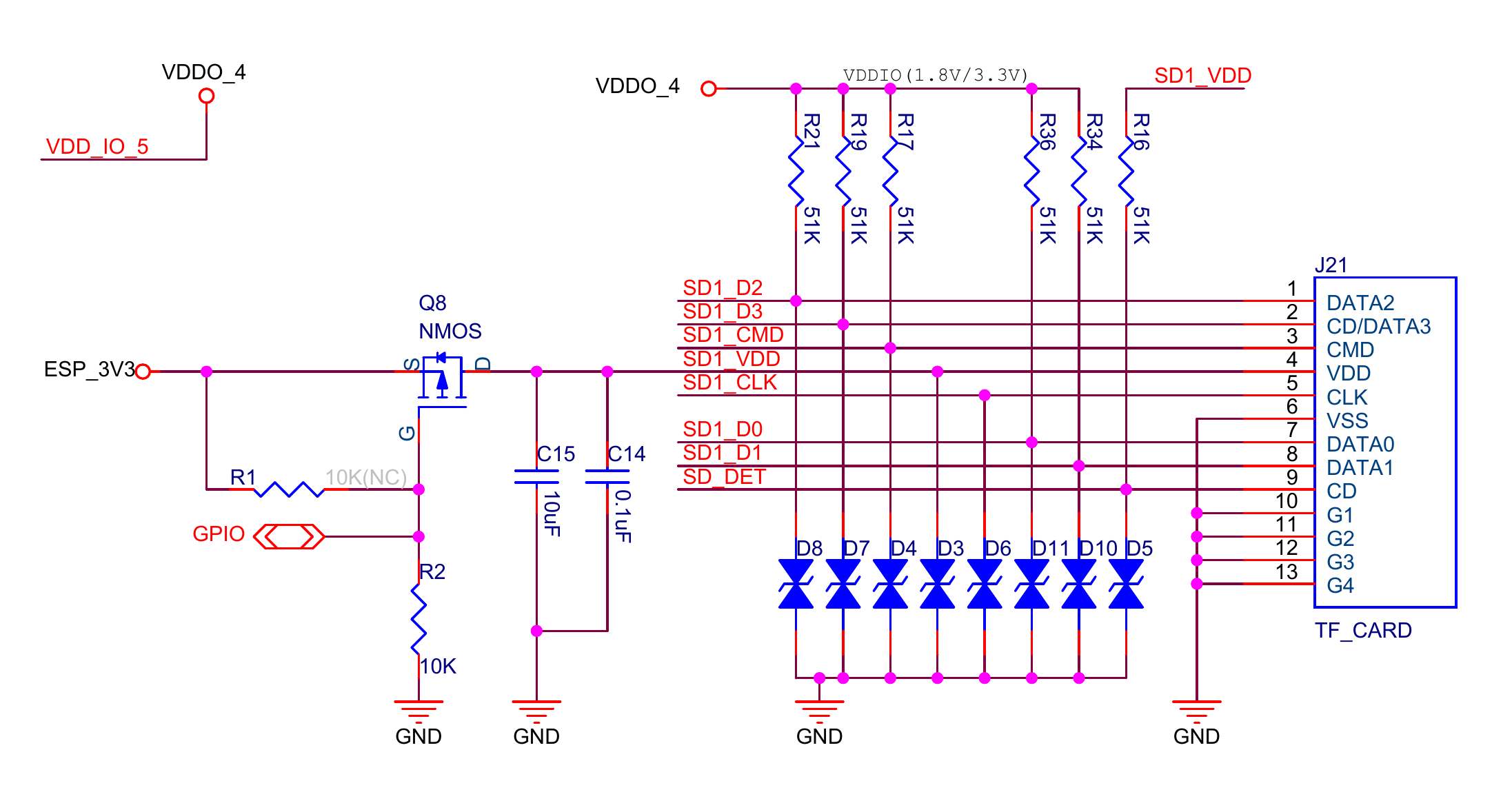

SDIO

ESP32-P4 系列芯片集成一个 SD/MMC 主机控制器,不能用做从机。该 SD/MMC 主机外设共有两个卡槽 (slot),用于插入 SD 卡、连接 SDIO 设备或连接 eMMC 芯片,每个卡槽均可单独使用。

卡槽 1 (SDMMC_HOST_SLOT_0) 信号通过 IO MUX 固定在下表中的 GPIO 管脚,专用于 UHS-I 模式。

SDIO 信号 |

管脚名称 |

|---|---|

SD1_CDATA0_PAD |

GPIO39 |

SD1_CDATA1_PAD |

GPIO40 |

SD1_CDATA2_PAD |

GPIO41 |

SD1_CDATA3_PAD |

GPIO42 |

SD1_CCLK_PAD |

GPIO43 |

SD1_CCMD_PAD |

GPIO44 |

SD1_CDATA4_PAD |

GPIO45 |

SD1_CDATA5_PAD |

GPIO46 |

SD1_CDATA6_PAD |

GPIO47 |

SD1_CDATA7_PAD |

GPIO48 |

卡槽 2 (SDMMC_HOST_SLOT_1) 信号通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚,这适用于非 UHS-I 用途。

请在 SDIO GPIO 管脚处添加上拉电阻,建议每根线上预留一个串联的电阻,并在 SDIO CLK 线上预留对地的电容用于调节。

考虑到 SDIO 3.0 协议中 SDIO GPIO 工作电压自动切换的要求,建议把 SDIO GPIO 的电源域 VDD_IO_5 和外部上拉电源连接至 VDDO_4。SD 卡供电电源请连接至系统 3.3 V 电源。

ESP32-P4 SD 3.0 卡电源电路图

为了降低 SD 卡的功耗和复位 SD 卡,可以在 SD 卡电源处预留 MOS 管电路,通过 GPIO 来控制。

USB

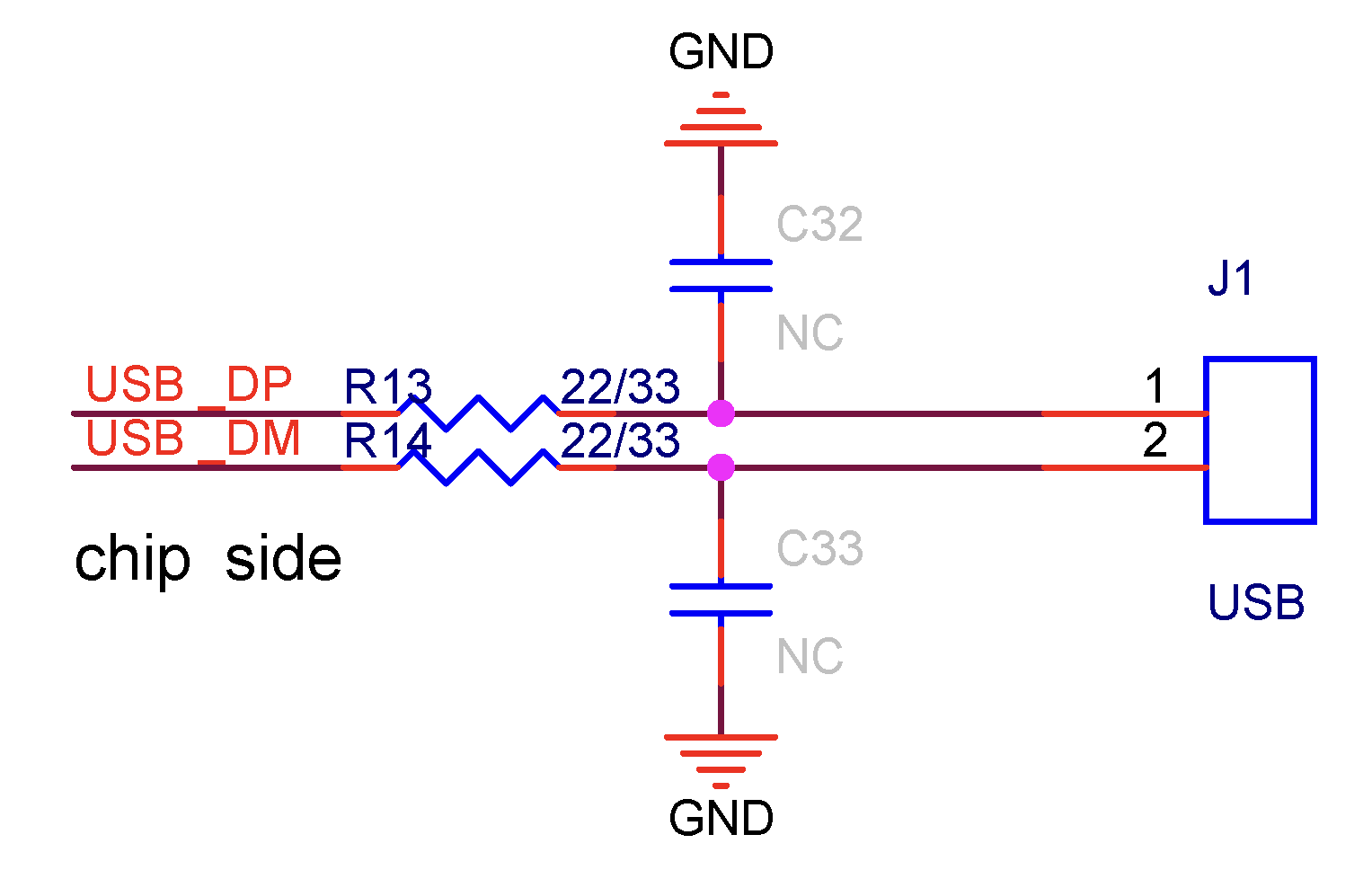

ESP32-P4 系列芯片集成一个 USB 串口/JTAG 控制器,默认使用 GPIO24 和 GPIO25 作为 USB 的 D- 和 D+。

ESP32-P4 系列芯片带有一个集成了收发器的全速 USB On-The-Go (OTG) 外设,符合 USB 2.0 规范,默认使用 GPIO26 和 GPIO27 作为 USB 的 D- 和 D+。

使用 USB 串口/JTAG 控制器和全速 USB On-The-Go (OTG) 外设时,请注意:

USB 的 D- 和 D+ 管脚功能可以互换。

使用单个功能时,可以选择 GPIO24/GPIO25 和 GPIO26/GPIO27 其中任意一组。

同时使用两个功能时,GPIO24/GPIO25 和 GPIO26/GPIO27 各自作为一个功能的两个管脚使用。

ESP32-P4 系列芯片带有一个集成了收发器的高速 USB On-The-Go (OTG) 外设,符合 USB 2.0 规范,DM 和 DP 分别作为 USB 的 D- 和 D+。

使用芯片版本 v1.0 和 v1.3(不推荐用于新设计)时,请在 DP 管脚处添加一个 1 MΩ 下拉电阻用于降低 CHIP_PU 拉低时 VDD_USBPHY 的脉冲大电流。

DP 下拉电阻(芯片版本 v1.0 和 v1.3)

在芯片版本 v3.0 和之后版本中,该问题已经被修复,可以保留 1 MΩ 下拉电阻用于兼容设计。

全速 USB 的 D- 和 D+ 线上建议预留串联电阻(初始值可为 22/33 Ω)和对地电容(初始可不上件),并注意靠近芯片端放置。

ESP32-P4 系列芯片 USB RC 电路图

建议在 USB 连接器端预留 ESD 保护二极管。当使用高速 USB OTG 外设时,请注意 ESD 保护二极管的寄生电容不能超过 1 pF,否则会导致信号质量较差,传输不稳定。

ESP32-P4 系列芯片也支持通过 USB 进行下载,请参考 下载指导。

触摸传感器

使用 TOUCH 功能时,建议靠近 ESP32-P4 侧预留串联电阻,用于减小线上的耦合噪声和干扰,也可加强 ESD 保护。该阻值建议 470 Ω 到 2 kΩ,推荐 510 Ω。具体值还需根据产品实际测试效果而定。

ESP32-P4 系列芯片的触摸传感器同时还支持防潮功能和遇水保护功能。防潮设计可缓和小水珠带来的影响,ESP32-P4 触摸传感器引入 Shield Pad 这一特殊 PAD。用户可以任选一个触摸管脚作为 Shield Pad,Shield Pad 会和当前正在测量的触摸管脚进行并联,有效缓和水滴带来的影响。

以太网 MAC

EMAC RMII 接口 GPIO 配置请见下表。

EMAC 信号 |

管脚名称 |

|---|---|

RMII_CRSDV |

GPIO28, GPIO45, GPIO51 |

RMII_RXD0 |

GPIO29, GPIO46, GPIO52 |

RMII_RXD1 |

GPIO30, GPIO47, GPIO53 |

RMII_RXER |

GPIO31, GPIO48, GPIO54 |

RMII_CLK |

GPIO32, GPIO44, GPIO50 |

RMII_TXEN |

GPIO33, GPIO40, GPIO49 |

RMII_TXD0 |

GPIO34, GPIO41 |

RMII_TXD1 |

GPIO35, GPIO42 |

RMII_TXER |

GPIO36, GPIO43 |

建议在 RMII CLK 线上预留串联电阻用于调节。

请注意 RMII 接口中的时钟信号仅为输入,如果要使用时钟输出的方案,请使用 REF_50M_CLK_PAD 信号 (GPIO23/GPIO39)。

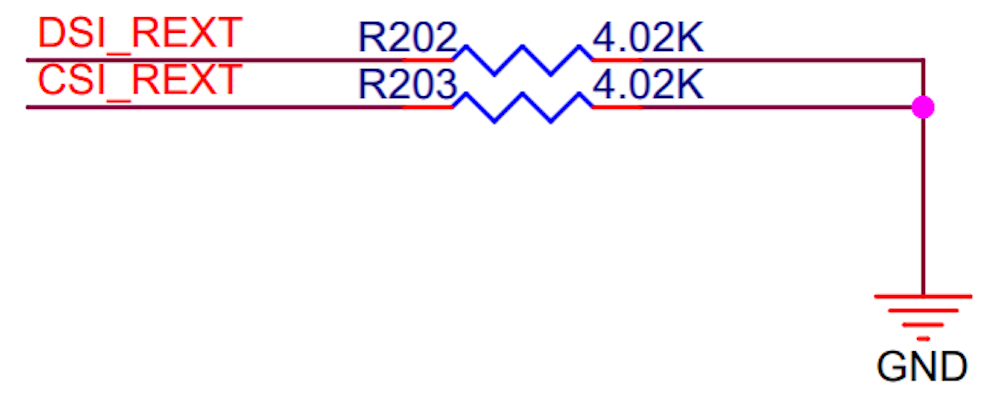

MIPI

ESP32-P4 带有一个 MIPI DSI 接口,用于连接 MIPI 接口的显示屏;它还带有一个 MIPI CSI 接口,用于连接 MIPI 接口的摄像头。请在 CSI_REXT 和 DSI_REXT 管脚处各添加 4.02 kΩ 下拉电阻。

建议在 MIPI 通信线上预留串联电阻(初始可使用 0 Ω),主要作用为降低驱动电流,调节时序,提升抗干扰能力等。

如果设计中有射频模块,请在 CSI 接口对接的设备端也添加串联电阻以降低对射频模块的干扰。

注意

如果不使用 MIPI 接口,电源和外置电阻管脚可以悬空。

对于 MIPI 接口的设备,其控制信号请使用 GPIO。

ESP32-P4 MIPI 信号电路图